# A C-to-FPGA Solution for Accelerating Tomographic Reconstruction

Nikhil Subramanian

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering

University of Washington

2009

Program Authorized to Offer Degree: Department of Electrical Engineering

#### University of Washington

#### Abstract

#### A C-to-FPGA Solution for Accelerating Tomographic Reconstruction

Nikhil Subramanian

Chair of the Supervisory Committee: Professor Scott A. Hauck Electrical Engineering

Computed Tomography (CT) image reconstruction techniques represent a class of algorithms that are ideally suited for co-processor acceleration. The Filtered Backprojection (FBP) algorithm is one such popular CT reconstruction method that is computationally intensive but amenable to extensive parallel execution. We develop an FPGA accelerator for the critical backprojection step in FBP using a C-to-FPGA tool flow called Impulse C. We document the strategies that work well with Impulse C, and show orders of magnitude speedup over a software implementation of backprojection. We contrast the ease of use and performance of Impulse C against traditional HDL design, and demonstrate that Impulse C can achieve nearly the same performance as hand coded HDL while significantly reducing the design effort.

# TABLE OF CONTENTS

| List of Figures                                  | iii |

|--------------------------------------------------|-----|

| List of Tables                                   | iv  |

| Chapter 1 Introduction                           | 1   |

| Chapter 1 Introduction                           | 1   |

| Chapter 2 Background                             |     |

| 2.1 Tomographic Reconstruction                   | 3   |

| 2.1.1 CT Systems                                 |     |

| 2.1.2 Filtered Backprojection                    |     |

| 2.1.3 Backprojection                             |     |

| 2.2 Coprocessor Accelerators                     | 11  |

| 2.2.1 Coprocessor Acceleration of Backprojection |     |

| 2.2.2 Field Programmable Gate Arrays             | 14  |

| 2.2.3 FPGA Accelerator Platforms                 |     |

| 2.3 C-to-FPGA Design Tools                       | 17  |

| 2.3.1 Impulse C                                  |     |

| Chapter 3 Design Considerations                  | 23  |

| 3.1 From C to Impulse C                          | 23  |

| 3.1.1 Filtered Backprojection Software Benchmark | 23  |

| 3.1.2 Porting to Impulse C                       |     |

| 3.2 Refactoring Code for Hardware Generation     | 29  |

| 3.2.1 Index Generation through Offsets           | 32  |

| 3.2.2 Fixed Point Representation                 |     |

| 3.2.3 Pipelined Data Path                        |     |

| 3.3 Design Architecture                          | 43  |

| 3.3.1 Parallel Design Architecture            | 43 |

|-----------------------------------------------|----|

| 3.3.1.1 Loop Unrolling                        | 44 |

| 3.3.1.2 Memory Utilization                    | 46 |

| 3.3.1.3 DSP Utilization                       | 47 |

| 3.3.2 System Level View                       | 48 |

| Chapter 4 Results                             | 50 |

| 4.1 Performance and Resource Utilization      | 51 |

| 4.2 Impulse C Vs Software                     | 54 |

| 4.3 Impulse C Vs HDL                          | 56 |

| Chapter 5 Conclusions                         | 61 |

| 5.1 Writing Efficient Impulse C               | 61 |

| 5.2 The Strengths and Weaknesses of Impulse C | 62 |

| 5.3 Future Directions                         | 63 |

| 5.4 Conclusion                                | 64 |

|                                               |    |

|                                               |    |

| References |  |

|------------|--|

|------------|--|

# LIST OF FIGURES

| Figure 1.1 Simplified Tomography Flow                           |    |

|-----------------------------------------------------------------|----|

| Figure 2.1 CT System                                            |    |

| Figure 2.2 Reconstruction                                       | 5  |

| Figure 2.3 Backprojection                                       | 5  |

| Figure 2.4 Backprojection with and without filtering            | 6  |

| Figure 2.5 Flow of operations in software implementation of FBP | 7  |

| Figure 2.6 Image Pixels contributing to detector values         |    |

| Figure 2.7 Backprojecting along rays                            | 9  |

| Figure 2.8 XD100 Development System                             |    |

| Figure 2.9 CoDeveloper Application Manager Screenshot           |    |

| Figure 2.10 Design flow to target XD1000 with Impulse C         |    |

| Figure 3.1: Data rates to Shared Memory                         | 27 |

| Figure 3.2 Configuration Function code snippet                  |    |

| Figure 3.3 Backprojection code from SW benchmark                |    |

| Figure 3.4 Loop Reordering                                      |    |

| Figure 3.5 Offset-based index generation                        |    |

| Figure 3.6 Detector offsets when walking through image          |    |

| Figure 3.7 Detectors in the image space                         |    |

| Figure 3.8 Pipelining the backprojection code                   |    |

| Figure 3.9 Impulse C Stage Master Explorer                      | 41 |

| Figure 3.10 Pipelined and Parallel Data Path                    | 45 |

| Figure 3.11 System Architecture                                 |    |

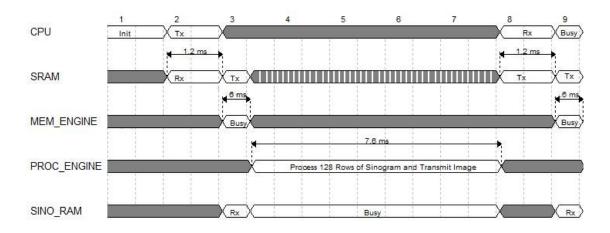

| Figure 4.1 System timing for CPU accumulation                   | 51 |

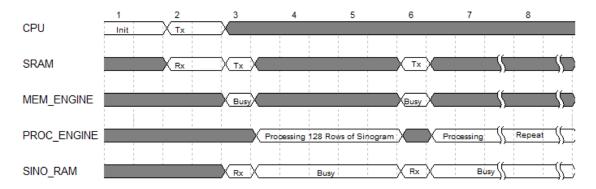

| Figure 4.2 System timing for FPGA accumulation                  |    |

# LIST OF TABLES

# ACKNOWLEDGEMENTS

I would like to thank the Washington Technology Center (Seattle, WA) and Impulse Accelerated Technologies (Kirkland, WA), for the funding that made this research possible. Many thanks to Adam Alessio for providing expert guidance and the FBP software benchmarks; and Jimmy Xu for being a patient co-worker and creating the HDL version of the design. I would like to express my deepest and most sincere gratitude to my advisor, Professor Scott Hauck, for being a source of tremendous inspiration. Finally, I would like to thank my family for their constant support and encouragement; without them, this thesis could not have been completed

# 1. Introduction

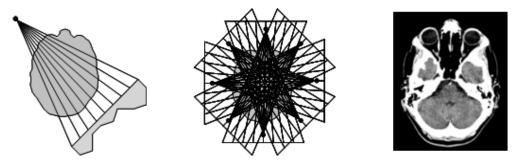

Computed Tomography (CT) is a medical imaging technique used to create crosssectional images from x-ray transmission data acquired by a scanner. In tomographic systems, the primary computational demand after data capture by the scanner is the backprojection of the acquired data to reconstruct the internal structure of the scanned object (Figure 1.1). Backprojection can be viewed as the mapping of raw data into the image space and has a complexity of  $O(n^3)$  when generating 2D cross-sections and  $O(n^4)$  for full 3D reconstruction. In a typical CT system, the data has ~10<sup>6</sup> entries per cross-section and the process of tracing each datum through the image space is demanding. As a result, hardware acceleration of this process has been the focus of numerous studies.

Figure 1.1 Simplified Tomography flow. Scanning (left) produces a set of aggregate data on probe lines. Through backprojection (center) multiple samples are brought together to reconstruct the internal structure of the patient (right).

Previous work on backprojection [3-10] has shown that hardware accelerators can achieve much higher performance than microprocessor-based systems. Field Programmable Gate Arrays (FPGAs) are often used to build such accelerators. The traditional way to design an FPGA-based accelerator is to describe the hardware performing the computation using a schematic or a hardware description language (HDL). For some years now there has been interest in C-to-FPGA tool flows that allow users to describe the computation in C and automatically generate the hardware description. This makes the process of creating FPGA designs easier and allows for wider adoption of FPGAs, even by those with little or no hardware engineering expertise.

The general perception has been that while such high level tool flows are simple to use, they do not provide the same level of performance as hand coded HDL. We investigate this notion by profiling a C-to-FPGA tool flow called Impulse C (Impulse Accelerated Technologies, Kirkland, WA, USA). Our software benchmark was an implementation of the filtered backprojection (FBP) algorithm running on a processor. We partitioned the design such that the compute intensive backprojection step was run on an FPGA while the user interface and some filtering operations were performed on the host processor. The XD1000 (XtremeData Inc., Schaumburg, IL, USA) development system was chosen for the implementation because it offers a tightly coupled CPU-FPGA platform. Details of the Impulse C tool flow and the XD1000 development system can be found in Chapter 2.

This thesis provides a case study on how a C-to-FPGA tool flow can be used to design an efficient FPGA-based accelerator by documenting some of the strategies that work well and some common pitfalls to avoid. It is organized as follows:

- Chapter 2: Background introduces the filtered backprojection algorithm, FPGA-based accelerators and the Impulse C tool flow.

- Chapter 3: Design Considerations discusses issues related to porting a design to Impulse C and also describes the implemented FPGA design.

- Chapter 4: Results presents the performance of the various versions of the design in comparison to software and hand coded HDL.

- Chapter 5: Conclusions is a summary of the lessons learned and a discussion of possible future research.

# 2. Background

#### 2.1. Tomographic Reconstruction

Tomographic reconstruction is the process of generating cross-sections of an object from a series of measurements acquired from many different directions. In Computed Tomography (CT or "CAT" scans), the measurements are x-ray attenuation data. We now discuss CT systems and the reconstruction process.

#### 2.1.1. CT Systems

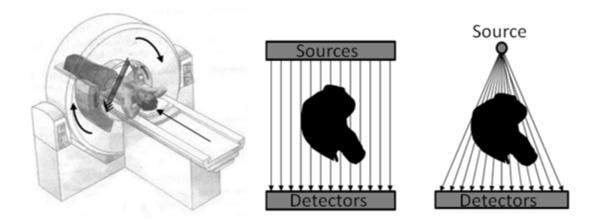

A CT system comprises of a scanner that is housed in a radiation safe scanning room and an adjoining computer suite to generate, view and print images. The scanner has a movable platform and a ring shaped gantry that carries x-ray sources on one side and detectors on the other side. The gantry rotates about an axis perpendicular to the platform, enabling measurements at various angles. The sources and detectors in the gantry can come in two configurations, leading to distinct beam geometries. The simpler of these is the parallel beam geometry, which arises from a linear array of sources and detectors. Fan beam geometry is the result of a single source and a linear array of detectors.

Figure 2.1 CT System. Scanner [14] with movable patient platform and ring shaped rotating gantry. Parallel Beam (center) and Fan Beam (right) geometry.

Patients lie down on the platform, which is moved into the gantry to position the scan area in the path of the x-rays. The sources then generate and direct x-rays through the patient. Different parts of the human anatomy, such as bones and soft tissue, attenuate the incident x-rays by varying amounts. The detectors record the received intensity. The set of detector intensity readings for any angle is called a projection. The gantry rotates and collects several projections at equidistant angles over a 180-360 degree span. From this set of projections a single image slice can be generated. In a typical CT exam, multiple closely spaced image slices are generated to image an entire organ.

First generation CT scanners consisted of a single source and single detector. Both the source and detector needed to translate to collect a single projection; then the source/detector mechanism rotated to collect more projections. In second generation CT scanners, multiple detectors were included to reduce the number of translations and rotations required. Third generation CT scanners have a large array of detectors opposite a single source on a fixed rotating gantry; these scanners do not require a translating step leading to dramatically reduced scan times. Fourth generation CT systems have a fixed detector array that completely surrounds the patient; only the CT tube rotates. The increased sophistication of modern scanners naturally increases the complexity of the reconstruction process; however, the core computation is still conversion of the detector data into an image. One way to solve the image reconstruction problem is with the popular filtered backprojection (FBP) algorithm.

#### 2.1.2. Filtered Backprojection (FBP)

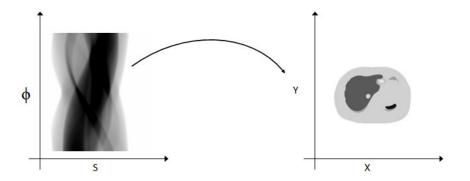

The set of all projections acquired by a scanner is a two dimensional matrix of data. This data represents a 2D spatial function termed a sinogram, because each point in the image has contributions from several points that lie on a sine wave in the 2D spatial function. The problem of reconstruction can be viewed as the problem of transforming the sinogram into the image space (X,Y). A plot of the

sinogram data on a grayscale is shown in figure 2.2 (left). The simplest way one can imagine solving this is through backprojection which is also known as the summation method or linear superposition method.

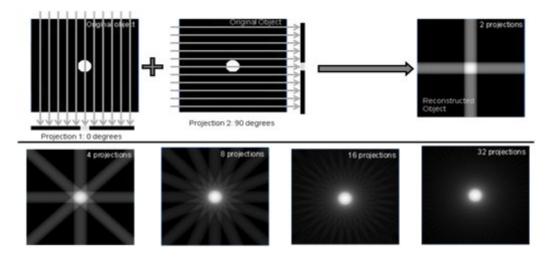

Figure 2.2 Reconstruction [17]. Transformation from sinogram (left) to image space (right) Backprojection simply reverses the measurement process and can be thought of as smearing the projections back across the reconstructed image. Figure 2.3 below provides some intuition for how this works. In the simplest case, projections are taken in only two orientations. The reconstruction is obtained by wiping each projection back across the image at the angle at which it was acquired. The additive effect of overlapping regions makes those parts of the image brighter.

Figure 2.3 Backprojection [18]. In the simple case an image can be generated from just two projections (top). Images generated from 4, 8, 16 and 32 projections (bottom)

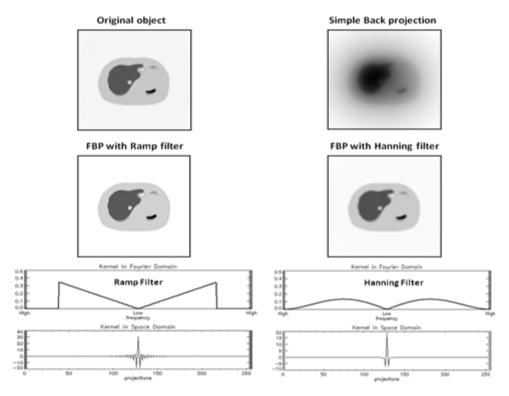

As seen in figure 2.3, more projections give a better reconstruction. However, even for a large number of projections, there is blurring around the object. The streaking and star-like artifacts in the image arise because backprojection is not the exact inverse operation of the image acquisition process. To eliminate the low frequency blur, the acquired data (sinogram) is high-pass filtered before backprojection. This is Filtered Backprojection (FBP). The Ramp Filter is often used in FBP because it provides ideal reconstruction in the absence of noise [11]. If noise is present, the Ramp Filter leads can lead to excessively noisy images because it accentuates the high frequency components in the data. Since measured data can contain some noise, the Ramp Filter is often apodized to reduce high frequency contributions. Smooth apodization filters are generally better when viewing soft tissue and sharper filters aid high resolution imaging. Figure 2.4 shows the difference in image quality when backprojection is performed with and without filtering.

Figure 2.4 Backprojection with and without filtering [17]

The flowchart (figure 2.5) below shows the sequence of operations involved in a simple software implementation of FBP. There is strong motivation to accelerate the backprojection stage that has a computational complexity of  $O(n^3)$ .

Figure 2.5 Flow of operations in software implementation of FBP

The transformation of generating a sinogram by taking line integrals through the image is known as the x-ray transform which in two dimensions is the same as the Radon transform. FBP is one analytical reconstruction method to implement the inverse Radon transform. Reconstruction can also be performed through other analytic image reconstruction techniques such as Direct Fourier Methods or iterative reconstruction techniques such as Maximum-Likelihood Expectation-Minimization (ML-EM). For a formal mathematical treatment of the analytical and iterative image reconstruction concepts, the reader is directed to this excellent reference [1].

### 2.1.3. Backprojection

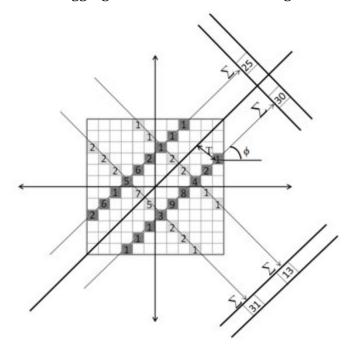

As mentioned earlier, different parts of the scanned object attenuate the incident x-rays by varying amounts. Thus, the scanning process can be modeled as detectors acquiring line integrals of the attenuation along the scanned object. Figure 2.6 shows this model of data acquisition in the image space. The value of an image pixel is proportional to the attenuation at that point. The highlighted pixels along the ray contribute to the measured value, which we will call the "ray-value". These values are aggregated as entries of the sinogram.

Figure 2.6 Image Pixels contributing to detector values

When reconstructing, we start with an image initialized to 0. Corresponding to each entry of the sinogram (i.e. a ray-value) we identify all the pixels that lie on the ray. The values of those image pixels are then incremented by the corresponding ray-value (figure 2.7). When this process is performed for all entries in the sinogram, we have reconstructed the image. This is ray-by-ray reconstruction. Another way to approach this is to reconstruct one pixel at a time. In this scheme, given a pixel and an angle of measurement, the ray-value that

contributes to the pixel needs to be identified. If we go through all angles, identifying all rays that the pixel was on, and add the ray-values together, that pixel is fully reconstructed. We can then go ahead and reconstruct all the other pixels in the same way. This is pixel-by-pixel reconstruction.

Figure 2.7 Backprojecting along rays

The ray-by-ray and pixel-by-pixel methods produce identical results, and primarily differ in their implications for resources required for implementation. We will carry forward the discussion with the pixel-by-pixel method, realizing that similar concepts apply to the ray-by-ray approach.

When we reconstruct a pixel at a time, the operation that was informally introduced as "smearing" projections back across the image actually involves summing the detector values that contributes to the pixel at each angle. Recall that the sinogram is a 2D matrix with a row of detector values for each angle. Hence, we need the index of the detector value that contributes to the pixel being reconstructed. For a given pixel (x,y) and angle *theta*, the index of the sinogram entry that contributes to that pixel value can be identified using the formula

$$T = x^{*}\cos(theta) + y^{*}\sin(theta)$$

The value of T derived from the computation above does not always result in a unique integer index corresponding to a single ray-value. For example, if T=3.7, the value at index 3 and at index 4 contribute to the image pixel. The fractional part of T (.7 in this case), is used to perform interpolation between the two ray values at index 3 and 4.

The computations involved in reconstructing a pixel are: simple trigonometry to find detector index for each angle, interpolation and accumulation. These procedures by themselves are simple. The computational complexity of FBP does not stem from the complexity of the individual operations, but rather from the sheer number of them. CT scanners acquire between 512 and 1024 projections (with ~1024 entries each) per slice, and so reconstructing a pixel involves performing the computations 512 – 1024 times. Typically 512x512 images are reconstructed, and thus during backprojection each pixel in a 512 by 512 matrix goes through 512-1024 of the simple computations mentioned above.

There is further motivation to focus on the acceleration of backprojection. Filtered backprojection produces the correct reconstructed image from noisefree, continuous data. However, the acquired data in tomographic systems are subject to various random phenomenon and irregularities which FBP does not account for. In order to employ a "closer to real" model of the acquisition process, iterative techniques are employed [15]. From a computation standpoint, these techniques involve repeated transformations between the image space and the projection space in contrast to FBP which makes just one transform of the projection data into the image space (with associated filtering). As a result, depending on the number of iterations used, iterative techniques can be orders of magnitude more computationally demanding than FBP. In FBP, backprojection accounts for 70-80% of the total execution time. In iterative techniques, backprojection and forward projection can account for as much as 70% to 90% of the execution. As a result hardware acceleration of the backprojection and the forward projection step has been the focus of numerous studies [3-10].

# 2.2. Coprocessor Accelerators

Frequently occurring or complex computations can overwhelm the primary microprocessor (host or CPU) in a computer system. While the host processor performs useful functions such as the user interface and interfacing with peripherals, a coprocessor is better suited to undertake heavy workloads. The most common coprocessor is the Graphics Processing Unit (GPU), also known as a Graphics Card or Graphics Accelerator. GPUs are specially designed chips used to accelerate 3D graphics rendering and texture mapping. With the proliferation of high definition computer displays and rich 3D content, their utility is justified in most modern computing scenarios.

With increasing demand for higher computational performance and increased power efficiency, there are many new and promising coprocessor technologies. The Cell Broadband Engine (CBE) (IBM Corporation, Armonk, NY, USA), is a novel general purpose architecture optimized for distributed computing and is suitable for performing data parallel operations [5]. The Ambric (Nethra Imaging Inc., Santa Clara, CA, USA) is a Massively Parallel Processor Array (MPPA) with 336 processing cores that process data in parallel. It is a streaming architecture with an asynchronous array of processors and memories. These coprocessors can accelerate a wide variety of applications.

For custom or "niche market" computations that require acceleration, an off-theshelf coprocessor might not provide adequate performance or have the desired power efficiency. For such applications, there are two choices. The first is to design a full custom Application Specific Integrated Circuit (ASIC), which is a piece of custom silicon that can perform the computation. For any given computational task, a well designed ASIC fabricated in the current process technology will provide the best performance. However, this performance comes at a very high cost that can, usually, only be offset by large scale mass production of the design. Since the economic model of a "niche market" computation might not lend itself to mass production, people turn to another choice - Field Programmable Gate Arrays (FPGAs).

FPGAs are prefabricated Integrated Circuits (ICs) that can be programmed and reprogrammed to implement arbitrary logic. The logic circuit to be implemented is usually described using a Hardware Description Language (HDL), which is mapped to the resources on the FPGA by a compiler. Modern FPGAs have millions of gates of logic capacity, millions of memory bits and may even contain one or more embedded microprocessors. Although FPGA performance generally does not rival that of an ASIC, they can provide much higher performance than a standard processor for complex computing tasks. The advantage of FPGAs is that they do not have the prohibitively high costs associated with creating and fabricating ASICs. Hence FPGAs are often used to implement custom coprocessor accelerators.

#### 2.2.1. Coprocessor Acceleration of Backprojection

One of the obvious observations about backprojection is that the reconstruction of any one pixel is completely independent of any other. Thus, multiple pixels can be reconstructed in parallel on hardware that supports parallel processing. This is pixel parallelism. The other option is to reconstruct a single pixel from multiple projections in parallel. This is projection parallelism. An n-way parallel system (pixel or projection parallelism) is n times faster than a system that processes one pixel or one projection at a time. However, there is a significant difference in the required memory bandwidth. If n pixels are reconstructed in parallel, pixel parallelism requires n times the memory bandwidth required for the reconstruction of a single pixel, whereas projection parallelism does not require higher bandwidth than a non-parallel implementation [3].

On an FPGA, projection parallelism can be easily exploited. By pipelining the trigonometry, interpolation and summing operations we can further increase the number of operations running in parallel. An FPGA implementation of a 16-way projection parallel implementation with a 7 stage compute pipeline was demonstrated by Leeser et al. [3]. The implementation was on an Annapolis Micro Systems Firebird board comprising one Xilinx Virtex2000E FPGA chip and 36 Mbytes of on board SRAM. They could process a 512x512 image from 1024 projections in 250ms, which represented over 100x speedup compared to their software implementation running on a 1GHz Pentium.

GPUs have been employed to accelerate medical imaging reconstruction [7-10]. One of the main advantages of GPU as a co-processor is that they are relatively ubiquitous in computer systems. Xue et al. [7] demonstrated that backprojecting a 256x256 image from 165 equiangular projections having 512 detectors was 21x faster if implemented using 32 bit fixed point on an Nvidia GPU when compared to floating point on a CPU. Further, a 16 bit fixed point implementation on the same GPU was 44x faster than the CPU.

Table 2.1, adapted from Kachlerie $\beta$  et al. [5] below, shows the performance of the CBE in comparison with other custom hardware implementations of FBP The numbers in the table are scaled for the reconstruction of 512x512 images from 512 projections with 1024 detector channels and for advances in process technology. The table also shows the bit-width of the data path employed with i representing integer and f representing floating point. Agi et al. [4] demonstrated the first ASIC to implement backprojection. The ASIC performance is superior to

that of other custom hardware platforms for reasons described in the previous section. The custom hardware accelerators consistently outperform the software benchmarks in all the studies.

| Group                | Туре | Hardware             | Time   |

|----------------------|------|----------------------|--------|

| Leeser et al. [3]    | i09  | СРИ                  | 4.66 s |

|                      | i09  | FPGA (Virtex -2)     | 125 ms |

|                      |      |                      |        |

| Agi et al. [4]       | i12  | ASIC (1um)           | .7 ms  |

|                      |      |                      |        |

| Kachelrieß et al.[5] | f32  | CPU (reference)      | 5.2 s  |

|                      |      | Cell                 | 7.9 ms |

|                      |      |                      |        |

| Ambric [6]           | i16  | MPPA                 | 54 ms  |

|                      |      |                      |        |

| Xui et al. [7]       | f32  | СРИ                  | 7.13 s |

|                      | i32  | FPGA (Altera )       | 273 ms |

|                      | i32  | GPU (Nvidia GF 7800) | 295 ms |

Table 2.1 Custom hardware implementations of FBP [5]. Time taken to reconstruct 512x512 images from 512 projections; each having 1024 detector channels.

## 2.2.2. Field Programmable Gate Arrays

FPGAs come in various capacities, ranging from a few thousand gates of logic capacity, to several million. A designer makes the decision on which chip to use based on the requirements of the design. In FPGAs, speedup is not achieved by operating the design at very high clock frequencies, but rather by exploiting the parallelism in the design. Many signal processing and scientific computations have parallelism profiles that make them good targets for parallel computation.

FPGA resources often include distributed memories called Block RAMs, logic cells, registers, and hard wired digital signal processing (DSP) blocks. Each vendor uses different terminology to refer to these resources. This thesis uses the Altera (Altera Corporation, San Jose, CA, USA) names for FPGA resources. Other

FPGA vendors generally have comparable functionality in their chips. The Stratix series is Altera's range of high-end chips, and is frequently used in high performance computations.

| Device Family                | Stratix             | Stratix II           | Stratix III          | Stratix IV            |

|------------------------------|---------------------|----------------------|----------------------|-----------------------|

| Year of Introduction         | 2002                | 2004                 | 2006                 | 2008                  |

| Process Technology           | 130 nm              | 90 nm                | 65 nm                | 40 nm                 |

| Equivalent Logic<br>Elements | 10,570 to<br>79,040 | 15,600 to<br>179,400 | 47,500 to<br>338,000 | 105,600 to<br>681,100 |

| Adaptive Logic<br>Modules    | N/A                 | 6,240 to 71,760      | 19,000 to<br>135,200 | 42,240 to<br>272,440  |

| Total RAM (Kbits)            | 899 to 7,253        | 410 to 9,163         | 1,836 to<br>16,272   | 8,244 to<br>22,977    |

| DSP Blocks                   | 6 to 22             | 12 to 96             | 27 to 112            | 48 to 170             |

Table 2.2 Altera Stratix series [19]

The basic building block of logic in an FPGA is a "slice", which contains look up tables (LUTs) to implement combinational logic, registers to implement sequential logic, and in many cases a carry chain to implement adders. Altera calls this an Adaptive Logic Module (ALM) in its Stratix series of FPGAs. The term adaptive comes from the fact that the ALM can be put in different modes that gives it flexibility to implement arithmetic between the LUTs in the ALM or certain many-input combinational functions with input sharing.

The Block RAMs in FPGAs come in various capacities. Altera calls its largest onchip memory M-RAM, each of which has 576 Kbits. There are a small number of these distributed around the chip. M4K RAM blocks, each of which has 4.5 Kbits, are much more widespread. There are also several instances of very small memories that are useful as local scratch space or to store constants. M512 RAM blocks are an example of these, and they have 576 bits each. Table 2.2 shows the total memory bits available in each Stratix chip. The memories can be configured as Single Port, Simple Dual Port, or True Dual Port. A Single Port memory can be read from or written to once every clock cycle. A Simple Dual Port memory can be written to and read from in the same cycle. In addition to this functionality, a True Dual Port memory can have 2 values written to it or read from it in a single cycle. The M512 memory blocks in the Altera chips can operate only in Single Port or Simple Dual Port mode. The M4ks and M-RAMs support all three modes.

The third important resource available in most FPGAs today is hard-wired DSP blocks, which are custom logic that implements DSP arithmetic more efficiently than ALM-based implementations. The Stratix-II DSP block can be configured either as one 36x36 multiplier, four 18x18 multipliers or eight 9x9 multipliers. They can also be configured to perform Multiply-Accumulate (MAC) operations, which are frequently encountered in DSP applications.

#### 2.2.3. FPGA Accelerator Platforms

The term "platform" is somewhat arbitrary, but generally refers to a known, previously verified hardware configuration that may be used as the basis for of one or more specific applications [12]. FPGA Accelerator Platforms have an FPGA coprocessor connected to a host through a high speed communication protocol. Traditionally, the utility of FPGA coprocessors was limited by the fact that the relatively slow links between the host and FPGA eliminated the gains achieved through acceleration. Today multi-gigabit, low latency communication links have made it attractive to offload data parallel applications. The Accelium platform made by DRC Computer and the XD development systems by XtremeData are good examples of devices with high capacity CPU-FPGA links. We chose the XD1000 development system for our implementation.

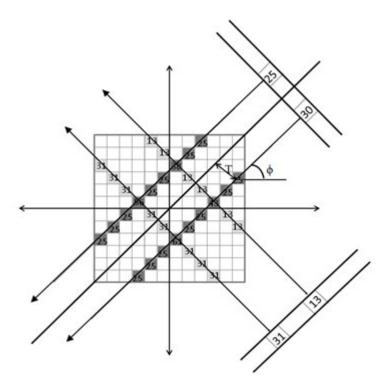

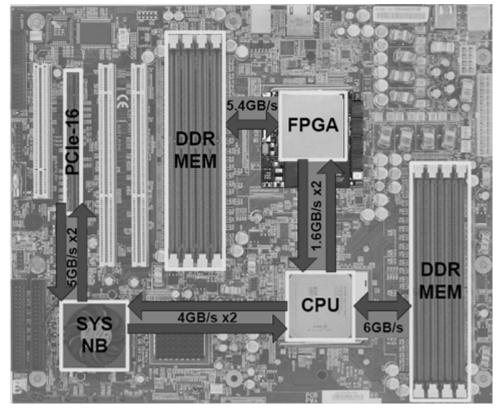

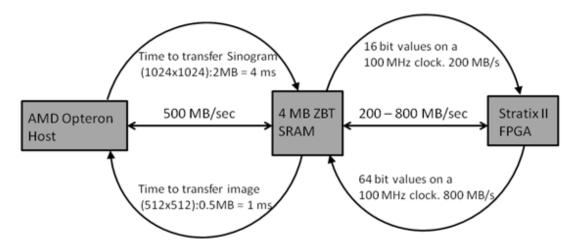

The XD1000 system has a dual Opteron® motherboard populated with one AMD Opteron processor and one XD1000 FPGA coprocessor module [13]. The

coprocessor module has an Altera Stratix II FPGA and a 4 Mbytes of SRAM. The coprocessor communicates to the CPU on the HyperTransport bus. Both the CPU and the coprocessor also have access to additional DDR3 RAM. Figure 2.8 shows the system architecture annotated with theoretical maximum data rates.

Figure 2.8 XD100 Development System [13]

## 2.3. C-to-FPGA Design Tools

FPGA designs are usually created by drawing a schematic or writing a hardware description in Verilog or VHDL. Current C-to-FPGA design tools allow users to create designs using C language semantics with added library functions to invoke specific hardware operations. The compiler generates HDL design files from the C code. Special compiler directives in the C code can be used to modify the outcome of the hardware generation process. Once the HDL is available, normal FPGA tool flows supplied by the FPGA vendor can be used to synthesize and map the design to the target chip.

The DK design suite by Agility Design Solutions Inc (Palo Alto, CA, USA) [24], the Mitrion-C compiler by Mitrionics, Inc (Lund, Sweden) [25], Catapult C by Mentor Graphics (Wilsonville, Oregon, USA) [26], and Impulse C by Impulse Accelerated Technologies (Kirkland, WA, USA) [27] are examples of commercially available C-to FPGA solutions. Our goal was to benchmark the performance of Impulse C against software and hand-coded HDL, and to provide a case study on how a C-to-FPGA flow might be applied to accelerate CT reconstruction.

#### 2.3.1. Impulse C

The Impulse C tools include the CoDeveloper C-to-FPGA tools and the CoDeveloper Platform Support Packages (PSPs). Table 2.3 gives a summary of the C-to-FPGA tools. PSPs add platform-specific capabilities to the Impulse CoDeveloper programming tools. With the PSP, users can partition the application between the host and coprocessors, make use of other on board resources, and automatically generate the required interfaces. The interfaces are implemented as a wrapper function around the user logic. We used the Impulse C tools (version 3.20.b.6) with the XtremData XD1000 PSP (version 3.00.a).

| Tool Name                       | Function                                                                   |

|---------------------------------|----------------------------------------------------------------------------|

| CoDeveloper Application Manager | Project Management and Design Entry.                                       |

| CoMonitor Application Monitor   | Monitoring designs as they execute.                                        |

| CoBuilder Hardware Generation   | Generate HDL from the C processes designated as "hw".                      |

| Stage Master Explorer           | Graphical tool to analyze effectiveness of compiler in parallelizing code. |

| Stage Master Debugger           | Graphical debugging tool to observe cycle-by-<br>cycle behavior of C code. |

Table 2.3 CoDeveloper C-to-FPGA tools

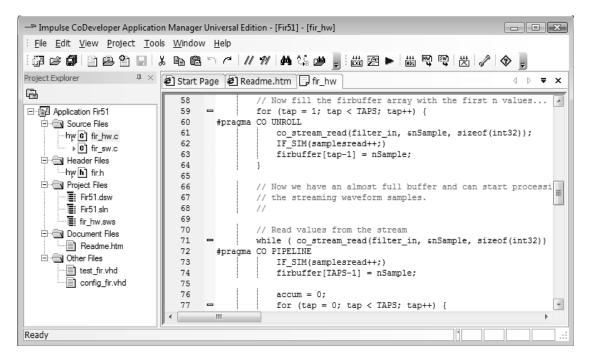

Figure 2.9 shows a screenshot of the Application manager. As seen in the figure, each source file is designated as "sw" or "hw" to indicate if they run on the host processor or on the FPGA. The files also have the " $\blacktriangleright$ " symbol just below the "sw"

or "hw" tag, indicating that they are targets for desktop simulation. Desktop simulation can simulate the entire design, including the interaction between software and hardware processes. While not cycle accurate, it is useful for functional verification of the design.

Figure 2.9 CoDeveloper Application Manager Screenshot

The CoMonitor Application Monitor allows the designer to observe the application as it executes by capturing messages, stream data values and other information. Code must be instrumented with special commands to indicate which variables and stream buffers need to be tracked by CoMonitor. Another useful tool is the Stage Master Explorer which is a graphical tool used to analyze how effectively the compiler was able to parallelize the C language statements. The tool also provides pipeline graphs, showing the estimated impact of various pipelining and compilation strategies.

CoBuilder generates synthesizable VHDL or Verilog only from processes in the files designated as "hw". It also generates various hardware/software interface

files, including a C runtime library and various hardware components that enable hardware/software communication on the XD1000. It creates a script that can be run to invoke Altera Quartus tools and synthesize the design. The software generation provides a software project directory that can be built and executed on the host Opteron processor.

The Impulse C programming model has two main types of elements: processes and communication objects. Processes are independently executing sections of code that interface with each other through communication objects. A software process is designated to run on a conventional processor and is constrained only by the limitations of the target processor. A hardware process is designated to run on an FPGA and is typically more constrained. It must be written using a somewhat narrowly-defined subset of C to meet the constraints of the Impulse CoBuilder FPGA compiler.

The following constraints are imposed on FPGA hardware processes [12]:

- a. No recursion. A hardware process or function may not call itself, either directly or indirectly.

- b. Limited use of function calls. A hardware process may call only the following types of C functions:

- Impulse C API functions (named co\_\*)

- Hardware primitive functions (using #pragma CO PRIMITIVE)

- External HDL functions

- c. Pointers must be resolvable at compile time

- d. Limited support for C structs

- e. No support for unions in C

Impulse C is designed for dataflow-oriented applications, but is also flexible enough to support alternate programming models including the use of shared memory as a communication mechanism. The programming model that is selected will depend on the requirements of the application and on the architectural constraints of the selected programmable platform target. A shared memory model is the preferred communication method between the host and FPGA on the XD1000 when using the Impulse C XD1000 PSP. Shared memory is implemented in the 4 MB SRAM found on the XD1000 module, and provides significantly better performance than streaming data between the CPU and FPGA.

In a software or hardware process, predefined Impulse C functions that perform inter-process communication may be referenced. These functions operate on communication objects to share data among processes. For example, read/write operations on a shared memory can be performed by calling functions on co\_memory objects within the processes. The Impulse CoBuilder compiler with XD1000 PSP generates synthesis compatible hardware descriptions (HDL code compatible with Quartus synthesis tools) for the Stratix II FPGA, as well as a set of communicating processes (in the form of C code compatible with the target crosscompiler) to be implemented on the Opteron processor.

Impulse C defines several mechanisms for communicating among processes, as shown in Table 2.4. Our FBP implementation on the XD1000 exclusively used shared memories to share data between the host and FPGA. We also employed signals for synchronization.

| Communication Object | Function                                      |  |

|----------------------|-----------------------------------------------|--|

| Streams              | Buffered, fixed-width data streams            |  |

| Signals              | One-to-one synchronization with optional data |  |

| Semaphores           | One-to-many synchronization                   |  |

| Registers            | Un-buffered data or control lines             |  |

| Shared memories      | Memory shared between hardware and software   |  |

Table 2.4 Impulse C communication objects [12]

Every Impulse C application has a configuration function which is used to define the overall architecture of the application. It includes the declaration of all processes and their communication. To use the communication mechanisms shown in figure 2.4, the programmer declares objects in the configuration function. Processes can take these objects as arguments and call functions on them to communicate with other processes. The processes and signals need to be statically configured at compile time (i.e. no new processes can be generated during the execution). The configuration function used in the FBP implementation is discussed in section 3.1.2.

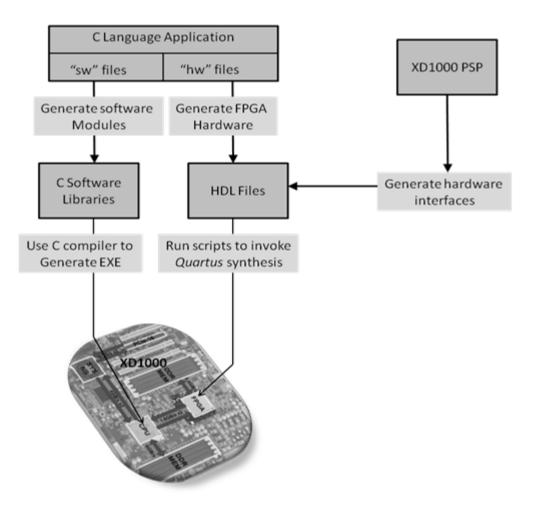

The summary of the Impulse C design flow to target the XD1000 is shown in figure 2.10.

Figure 2.10 Design flow to target XD1000 with Impulse C

# 3. Design Considerations

Acceleration on an FPGA is achieved by exploiting parallelism in the application. Designers need to consider how the hardware resources will be used by the computing elements and how the data flows through the system. Further, when partitioning a design across a host and coprocessor, the designer has to define how the host communicates and hands off the computation to the coprocessor. There is a tradeoff between the time it takes to transfer the data required to perform a certain computation and the acceleration that can be achieved by doing so.

### 3.1. From C to Impulse C

This section describes how Impulse C was used to accelerate the FBP software by partitioning the design between the host and FPGA on the XD1000 development system. The backprojection was carried out on the FPGA while the filtering, file I/O and other miscellaneous operations were performed on the CPU.

### 3.1.1. Filtered Backprojection Software Benchmark

The FBP software source code [20] is a C implementation of FBP compatible with parallel beam CT systems. It handles the file IO, and supports a variety of common filters. It uses 32-bit floating-point operations to perform computations. A floating-point implementation has sufficient precision to be considered nearperfect reconstruction in the absence of noise, and can be used as the standard to verify the accuracy of the hardware implementation. Table 3.1 summarizes the features of the FBP software source code.

| FBP Software Benchmark Features |                          |  |

|---------------------------------|--------------------------|--|

| Filters Supported               | Ramp, Hamming, Hanning   |  |

| Beam Geometry supported         | Parallel beam            |  |

| No. Of projections supported    | Adapts to input Sinogram |  |

| Image size produced             | User defined at run time |  |

| Data-path Width                 | 32-bit floating-point    |  |

| Interpolation Type              | Bi-linear                |  |

Table 3.1 FBP source code features

We profiled the software source code by running it on the 2.2 GHz Opteron-248 processor in the XD1000 system. Data from profiling the source code (table 3.2) shows that the backprojection is the slowest step, accounting for 70-80% of the execution time. The filter step accounts for most of the remaining execution time with the file I/O and miscellaneous operations account for less than 0.6%. Both the filter and backprojection operations are good targets for FPGA acceleration and could both be run on the FPGA, thereby utilizing the CPU for just the file I/O and miscellaneous operations.

Table 3.2 Software source code execution time for the reconstruction of a 512x512 image

| Execution Stage      | 512 Projections | 1024 Projections |

|----------------------|-----------------|------------------|

| Filter Stage         | 0.89 s          | 3.56 s           |

| Backprojection Stage | 3.85 s          | 10.03 s          |

| Misc and File IO     | 0.03 s          | 0.03 s           |

| Total Execution Time | 4.77 s          | 13.62 s          |

Efficient structures to implement high performance filters on FPGAs are well understood and are often provided by FPGA vendors as reference designs. Backprojection, on the other hand, brings up some interesting issues related to data flow, memory bandwidth and access patterns, making it a better choice for studying the performance of the Impulse C hardware generation process. As mentioned in section 2.1.3, there is additional motivation to focus on the acceleration of backprojection because of its utility in iterative reconstruction techniques. Based on these factors, we decided to offload only the backprojection to the FPGA coprocessor and have the rest of the application run on the Opteron processor. This required us to build an FPGA version of the backprojector, which we undertook with Impulse C. It also required the creation of Impulse C software processes to interface the computations running on the CPU with processes running on the FPGA.

It is worth clarifying why backprojection takes only 2.5 times longer when the number of projections is doubled (table 3.2), even though it is an O(n<sup>3</sup>) operation. The reason for this is that we reconstruct the same number of image pixels (512x512) in each case. As we move from 512 to 1024 projections, we increase the number of detector channels per projection from 512 to 1024 but this does not affect the number of computations performed as we are reconstructing pixel-by-pixel. In the base case (512 projections) shown in table 3.2 we perform (512x512x512) computations; in the other we perform (512x512x1024) operations. If we were to reconstruct a 1024x1024 image from 512 and 1024 projections, the backprojection stage would take 4 and 8 times longer respectively.

One of the important advantages of C-to-FPGA tools is the ability to reuse existing C codebases. The non-critical steps that are not targets for acceleration continue to run unmodified on the host. Only the functions that are targeted for acceleration need to be modified or rewritten to achieve an efficient implementation. We will use the term "refactoring" to refer to the process of modifying and reordering statements in a function in order to obtain an efficient hardware implementation. The next section describes the process of porting the above benchmark to the Impulse C framework. After that we discuss steps to refactor the backprojection function.

#### 3.1.2. Porting to Impulse C

The first step in porting a C application to Impulse C is to compile and run the existing code within the Impulse C framework. This is done by importing the code base and designating all source files as targets for desktop simulation. Desktop simulation simply compiles the application using a standard C compiler (gcc by default or a standard third-party compiler of the user's choice) into a native Windows executable that may be run directly or executed with a standard third-party debugger. Any ANSI compliant C code base should work in this framework. Once the existing code is in the framework, it is easy to add Impulse C processes to accelerate the desired functions.

The next step is to define the system level architecture (using a configuration function - see figure 3.2) and entry points for Impulse C processes. As mentioned earlier, based on the profiling data, we decided to implement the backprojection function as a hardware process on the FPGA. A software process is required on the host to interface with the hardware. The natural entry point for these processes is the function in the existing code that performs backprojection. That function can simply be replaced by a call to the Impulse C run-function. The run-function executes the software and hardware processes in the Impulse C application.

The software process serves as the bridge between the functions in the application and the computation executing on the FPGA. To the software process, we can pass both data structures from the C application and also the communication objects that enable CPU – FPGA interaction. Further, any global data structures or functions in the application are visible inside the software process. Once the hardware process has finished processing the data, the software process reads the results from the FPGA and presents it back to functions in the application that perform post processing and file output.

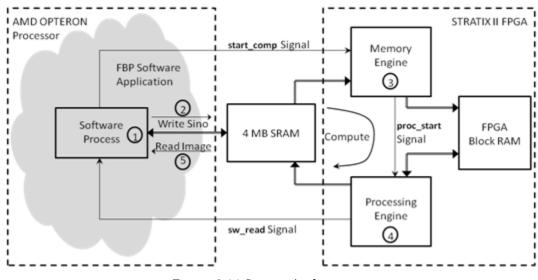

In the FPGA there are opportunities to overlap execution with memory accesses. With this in mind, the backprojector design is divided into two hardware processes. The "Memory Engine" performs memory accesses. The other, named "Processing Engine" performs the computations. This serves as a logical partitioning between the stages of execution.

Every Impulse C application running on a platform has one or more software processes running on the host and one or more hardware processes running on the FPGA. The system architecture that governs how they communicate among each other and synchronize their operations is largely determined by the architecture of the platform. It is also governed by the relative efficiency of different communication links on the platform. As mentioned in chapter 2, the most efficient dataflow model that Impulse C implements on the XD1000 platform is shared memory through the on-board SRAM. Based on this, we decided to go with the shared memory model for our application. Figure 3.1 shows the data transfer rates to the SRAM.

Figure 3.1: Data rates to Shared Memory

Comparing the transfer speed in figure 3.1 to the execution times in table 3.2, we see that the time it takes to move data to and from the shared memory is negligible compared to the time taken carry out backprojection in software.

Therefore, any acceleration that can be achieved by the FPGA implementation should speed up the overall execution. This is in contrast to situations where data transfer is slower than the execution time. In such cases, the decision to move the computation off-chip should be revisited.

Figure 3.2 shows the configuration function used to declare the various processes, signals, and shared memories in the design. As mentioned in section 2.3.1, the configuration function defines the architecture of the application.

```

void config_backproject(void *arg)

co_signal start_comp, sw_read, proc_start;

//Signals Declared

//Shared Memory Declared

co_memory shrmem;

co_process sw_proc, memengine, procengine;

//Processes Declared

//Create Signals

start_comp = co_signal_create("start_comp");

sw_read = co_signal_create("sw_read");

proc_start = co_signal_create("proc_start");

//Create Shared Memory - declare the memory size

shrmem = co_memory_create("data", "", MEM_SIZE);

//Create Processes - assign code bindings (co_function) and signals

sw_proc = co_process_create("cpu_proc" ,(co_function) SwProc, 3, shrmem, start_comp, sw_read);

memengine = co_process_create("fpga_mem",(co_function)MemEng, 3, shrmem, start_comp, proc_start);

procengine = co_process_create("fpga_proc",(co_function) ProcEng, 3, shrmem, sw_read, proc_start);

//Assign hardware processes to run on FPGA - PEO

co_process_config(memengine, co_loc, "PE0"); // Assign a hardware element

co_process_config(procengine, co_loc, "PE0"); // Assign a hardware element

```

Creating efficient code bindings for the hardware processes is crucial. It is this code that the compiler maps to HDL and is synthesized to run on the FPGA; its efficacy largely determines the achieved acceleration. The remainder of this chapter discusses issues pertinent to this task.

It is useful to clarify the following terms. In this thesis, we refer to the architecture of the entire system, including the CPU-SRAM-FPGA communication

interfaces, by the term "system architecture", and the architecture of the hardware design implemented on the FPGA as "design architecture".

#### 3.2. Refactoring Code for Hardware Generation

Figure 3.3 shows a code snippet (from the software source code) that performs backprojection. Pre-computed sine and cosine values are stored in arrays. The triple nested loop structure traverses the image pixel by pixel. The inner loop cycles through the angles and determines the index of the projections that contributes to the pixel for each angle. The values are then interpolated and added to the pixel.

```

void backproject(float **image, float **sinogramData, struct sino_info *sino, struct recon_image_info *geom)

float t_0, t, dat, findex, x, y, theta = 0.0;

int i, j, k;

float cs[NANGLES], sn[NANGLES]; /* Arrays to precompute cos(theta), sin(theta) */

float *im_pt;

/* Pointer to image[i][j]

* Precompute sin and cos for all projection angles */

for (k=0;k<NANGLES;k++)

sn[k]=sin(theta);

cs[k]=cos(theta);

theta+=(sino->angleSpacing);

}

/* Start Backprojection */

im_pt = &image[0][0];

t_0 = -0.5*(float)(sino->nProjs-1)*sino->projSpacing; /* Initial projection displacement */

y = t_0;

for (i=0;i<geom->yDim;i++)

Ł

x = t_0;

for (j=0;j<geom->xDim;j++)

for (k=0;k<NANGLES;k++)

t = y*cs[k]-x*sn[k]; /*For each image pixel determin the index of projection to accumulate*/

findex = (t - t_0)/sino->projSpacing;

dat = interpolate(findex, sinogramData, k);

/* Bi-linear interpolation between par. proj */

*im_pt += dat; /*Accumulate*/

} im_pt++;

x += geom->xPixelSize;

} y += geom->yPixelSize;

}

```

Figure 3.3 Backprojection code from SW benchmark

C code written to run on a processor does not automatically convert into an efficient FPGA implementation if passed without modification through the Impulse C hardware generation process. When hardware was generated from the code in figure 3.3 (after adding support for shared memory to enable communication), the resulting design was significantly slower than simply executing the code on the host processor. The code that eventually produces a good FPGA version must use the "special" resources (Distributed memories, DSP blocks etc) that enable parallelism on the FPGA. Obviously, if there is little or no parallelism, the FPGA cannot be faster at the task.

Loops in the C code are natural targets for parallel computation. A loop repeatedly performs the same computation on different pieces of data. If the hardware performing the loop computation is replicated as many times as the loop runs, the entire loop could theoretically be executed in the time it takes to perform a single iteration. This process is called loop unrolling. There might be dependencies that prevent parallel execution and care must be taken to avoid or work around these. Memory accesses inside the loop need to be streamlined because operations running in parallel cannot access the same memory at the same time. The memory either needs to broken up or replicated.

Loop unrolling in the context of hardware generation is not the same as the traditional software engineering loop unroll optimization where loops are unrolled to avoid loop overhead and gain limited execution overlap. In software execution there is no replication of the computing resources, whereas in hardware generation the data-path is replicated. In the hardware generation process, a loop with n iterations requires n times the resources when unrolled, but can be up to n times faster.

Loop unrolling is performed in Impulse C using the CO UNROLL pragma. Selecting the "Scalarize array variables" option during hardware generation replaces arrays (memories) by registers so that they can be accessed simultaneously. This works in simple cases. However, we might need the memories to be broken up into smaller memories instead of being converted into registers. In such cases, the CO UNROLL pragma may not be able to automatically generate the segmented memories required. Further, there may not be enough resources to completely unroll the loop. In such situations, we could partially unroll the loops. This might complicate the logic and memory structure. If there is a nested loop structure that needs to be partially unrolled with memory segmentation, CO UNROLL cannot be efficiently used. In such cases, we still have the option of manually defining separate smaller memories and manually performing a partial unroll of the loops. In our implementation the triple nested for-loop structure seen in figure 3.3 was partially unrolled by hand. This is described in more detail in the context of the design architecture in section 3.3.2.

Refactoring C code to implement parallelism generally involves unrolling loops and breaking up the memories (arrays in C code) such that they do not block each other. Another important optimization target is the inner loop computation itself. It is this computation that gets replicated in the process of unrolling, and so refactoring the code to produce the most efficient version of it is desirable. For example, in a system that is 128-way parallel, one adder saved in the inner loop computation saves 128 adders in the overall design. The inner loop computation can also be pipelined to increase the number of computations running in parallel. This is different from the parallelism execution achieved through loop unrolling. Unrolling creates identical copies of the data path that works simultaneously on independent data. On the other hand, pipelining allows different stages of the same data path to work simultaneously. Thus, pipelining and unrolling used together can provide higher speedup than using one or the other. The added advantage of pipelining the data path is that it increases the maximum frequency of operation of the design by breaking up the critical path. There are performance gains to be had if computations are performed in fixed point instead of floating point. Going to specific bit-widths for each operand can save resources. Other refactoring steps might include performing computations differently to save scarce resources. For example, if multipliers are a scarce resource in the system, any opportunities to save multipliers must be explored.

## 3.2.1. Index Generation through Offsets

Consider the code in figure 3.3. In the inner loop, the index of the projection (findex) that needs to be accumulated is determined. The fractional part of findex is used to perform Bi-linear interpolation, which requires 2 multipliers and an adder. In the code, determining findex requires two multipliers to find t and one constant denominator division operation to find findex (which can be implemented as a multiply). These three multipliers are used to generate each findex value. If we have n parallel computations, 3n multipliers get utilized in just determining the index of the projection that we need to interpolate. To avoid using these multipliers in computing findex, we generate findex values for each pixel through stored offsets instead of computing it.

One of the things to notice about the findex computations in figure 3.3 is that the variables x, and y are incremented by fixed amounts in the loop structure. Also,  $t_0$  and sino->projSpacing are constant values. Only the sine and cosine values change with the changing angles in the inner loop. However, if we reorder the loops such that the outermost loop traverses the projections, and the inner loops traverse the pixels, the angles remain constant in the inner loop. This reordering of the loops in figure 3.2 is shown in figure 3.4. Now, findex changes by a fixed amount in successive iterations of the inner loop.

Figure 3.4 Reordering loops from figure 3.2 Figure 3.5 Offset-based index generation

Instead of computing findex from scratch in each iteration, we can compute it by storing the initial value of findex and the fixed offsets for each angle. This provides a tradeoff between memory required to store the offsets and multipliers needed for findex generation. In our system multipliers in the form of DSP blocks were a scarcer resource than the small memories that would be needed to store the offsets, and hence we implemented the offset method of computing findex. Figure 3.5 shows the code that implements offset-based computing of findex. It is identical to the computation in figure 3.4. The initial value of findex for each angle is stored in the array INIT\_VALUE\_FINDEX. The arrays SIN\_X and COS\_Y store the horizontal and vertical offsets respectively. findex is computed by making appropriate offsets from the initial value.

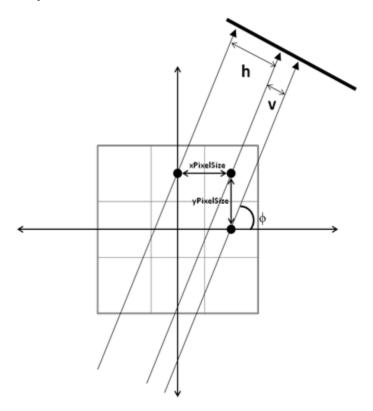

To gain some intuition for why the offset method works, consider what the inner loops do. For a given angle, the loops walk through the image pixels, figuring out where on the detector the x-ray through that pixel strikes. Figure 3.6 shows how for a given angle, the impact point on the detector varies for different pixels on the image. As we move horizontally across the image through a distance xPixelSize, the x-ray through the pixel strikes at a point h away on the detector bar. A vertical movement through a distance yPixelSize causes the x-ray to strike v away. h and v are related to xPixelSize and yPixelSize respectively through the simple trigonometric relationship

h = xPixelSize\*cos(*theta*),

v = yPixelSize\*sin(theta)

Figure 3.6 Detector offsets when walking through image

Thus, for each projection angle, if we know the position that the x-ray through the first pixel strikes the detector, and the value of hand v for that angle, we can determine where x-rays through neighboring pixels strike the detector. These positions are the values that index into projection data array, and are known as findex in the code snippets. For 512 projections we need to store 512 initial values, 512 v values and 512 h values. The memory required to store these values is less than 1% the total memory required by the design while the number of DSPs saved by this method is 50% of the total DSPs required by the design,

making it a very attractive tradeoff. Leeser et al. [3] use this index generation mechanism in their FPGA implementation.

#### 3.2.2. Fixed Point Representation

The advantage of floating point numbers over fixed point is the wide range of values they can represent. This advantage comes at the cost of complex logic required to implement floating point arithmetic. In applications where the range of values is not large, fixed point representation can be an equally accurate alternative to floating point. Standard C has no native data type to represent fixed point fractional data. One could implement fractional fixed point using ints by manually keeping track of where the decimal point is, but this is rarely done. Hence, in many C applications, floating point representations are used even when the data does not have the dynamic range to justify it.

The sinogram values that the FPGA operates on can be pre scaled to the range -1 to +1. In the backprojection stage, the sinogram values only get accumulated. Because we know the number of values that are added, we can determine a priori exactly what the theoretical maximum value of the accumulation will be. Based on this we can design the data path with fixed point arithmetic. Leeser et al. [3] performed a detailed study of the effects of quantization introduced through fixed point implementation of backprojection. They demonstrated that a 9-bit representation of the sinogram and 3-bit for the interpolation factor provided a good tradeoff between reconstruction quality and efficient implementation. In our implementation, we employed a more conservative approach using 16-bits to represent the sinogram and 16 bits for the interpolation factor. The internal arithmetic gives rise to 32 bit results (due to multiplying 16 bit numbers), and is scaled back to 16 bits by discarding the less significant bits.

We instrumented our floating point code to track the range and precision at different points of the data path. Table 3.3 shows bit width that was chosen for

different variables in the data path. A note about the notation (SsI.F) used. This implies there are S (1 or 0) sign bits, I integer bits and F fraction bits. The fixed point format for the sinogram data is 1s1.14. This means that there is one sign bit, one integer bit and 14 fraction bits. The variable floor is used to generate memory indices from findex. We selected different bit depths and visually assessed the influence on reconstructed images. We choose wide enough bit-widths to generate images with no discernable visual difference compared to the floating point implementation.

| Variable             | Format |

|----------------------|--------|

| Sinogram data        | 1s1.14 |

| Interpolation factor | 1s7.8  |

| Findex               | 1s10.8 |

| Floor                | 0s11.0 |

| Offsets              | 1s10.8 |

| Image data           | 1s8.7  |

Table 3.3: Fixed point format employed

By converting the sinogram data from 32 bit floating point to 16 bit fixed point, we need only half the number of DSPs to perform the interpolation step. This allows us to use the saved DSPs to accommodate more parallel operations, thus resulting in faster execution. The Stratix DSP block can multiply 16 bit fixed point numbers every cycle with no latency, whereas, floating point multiplication has 11 cycles of latency. Further, the fact that the fixed point representation of the sinogram and image are only half the size of their floating point counterparts makes the process of transferring them between the CPU and FPGA twice as fast. The result is that converting the design to fixed point results in at least a 2x speedup.

Impulse C supports fixed point via data types to represent data and macros to perform arithmetic on them. The data types are co\_intx/co\_uintx, where x represents the number of bits and int/uint represents signed and unsigned

numbers respectively. Impulse C also provides an efficient way to extract and insert bits into any position of a 32-bit number through the co\_bit\_extract and co\_bit\_insert functions. The macros only work on data types of certain bit-widths. In our implementation we extensively used the data types but preferred not to use the macros, choosing instead to manually track the number of fraction bits along the data path. Bits can be dropped using the standard C right shit operator ">>". In Impulse C, when making assignments of unequal bit-widths, bits of the same weight are preserved (i.e. if we assign a 32-bit variable to a 16 bit variable, the bottom 16 bits of the 32 bit number are copied to the 16 bit number). Using a combination of shifts and assignments, we can manually maintain data in the appropriate bit-width. Figure 3.8 shows the various fixed point operations used inside the computing loop.

The integer portion of the variable findex is the array index, and the fractional portion of it is the interpolation factor. All legal values of findex are positive. We however keep the sign bit because findex does come out negative for certain pixels that lie outside the field of view. In those cases, floor is an undefined index into the array (memory address). The image pixel is updated with some unknown value. This is not a problem because the pixels that lie outside the field of view are masked in a post processing step performed on the CPU. The compute pipeline (described next) is more efficient if the computation is performed on all image pixels; adding logic to the pipeline to avoid these corner cases reduces the achieved rate.

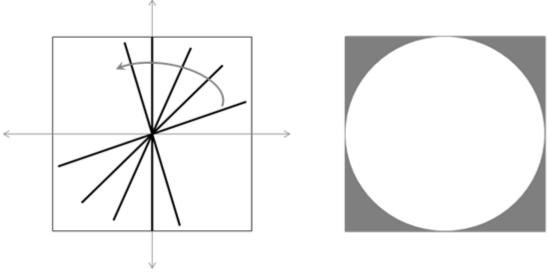

Figure 3.7 shows the field of view in the image. Only pixels lying in the inscribed circle lie in the field of view. This is because during reconstruction we assume that both the detector and the image are centered at the origin. When we rotate the detector through various angles, a circle is described. The points lying inside the circle are the valid pixels.

Figure 3.7 Detectors describe a circle in the image space (left). Valid pixels in the image (right).

## 3.2.3. Pipelined Data Path

We have discussed two optimizations of the inner loop computation (fixed point conversion and incremental computation of findex) and the benefit they provide. The next step is to pipeline the computation. Pipelining is the process of breaking up a complex computation into multiple stages so that the individual stages can run simultaneously. If each stage of the pipeline executes in 1 clock cycle and there are n pipeline stages, the first result from the pipeline is produced after n cycles. The time it takes for the first result to appear is called the latency of the pipeline. Every subsequent value from the pipeline is available in successive clock cycles (if there are no dependencies in the pipeline). For computations that are carried out many times in succession, the latency of the pipeline is negligible when compared to the time taken to produce all the results. Pipelining is accomplished in Impulse C using the CO Pipeline pragma.

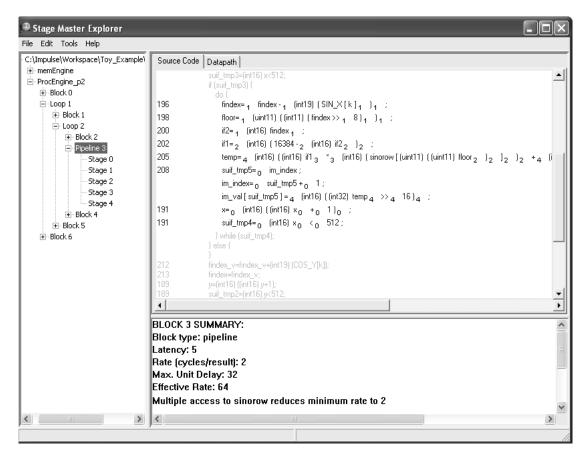

The Impulse C Stage Master Explorer tool is used to analyze the performance of pipelines in the design. It uses the following terms in the context of pipelining:

- Latency: The number of cycles for inputs to reach the output of the pipeline. It is equal to the number of stages in the pipeline.

- Stage Delay: The combinational delay or levels of logic in a single pipeline stage.

- Rate: The number of cycles after which the pipeline accepts new inputs. A rate of 1 means the pipeline accepts a new input every cycle. A Rate of r implies the pipeline accepts an input ever r cycles.

The Impulse C compiler groups all statements that can execute in parallel into a stage. All statements within a stage execute in one cycle. If there are many statements executing in a single stage, it results in a higher stage delay and lowers the maximum frequency of operation. If high frequency operation is desired, the stage delay of the pipeline can be constrained to equal a certain amount by using the CO SET stageDelay pragma. The compiler now only groups together those computations that can be performed within the specified stage delay. Another way to control how the stages are generated is using the co\_par\_break statement. This statement can be used to manually control which statements are grouped into a pipeline stage.

Figure 3.8 shows the backprojection loop with the pipeline pragma. This loop finds the contribution to every pixel in the image from one projection. The function call to interpolate() seen in figure 3.3-3.5, has been replaced by the actual interpolation code because Impulse C hardware generation has limited support for function calls. Further, it is easier to exercise control over the pipeline if all operations are visible in the loop. Interpolation requires 2 values to be fetched from memory, 2 multiplies and 1 add.

```

for(y=0;y<512;y++)

for(x=0;x<512;x++)

#pragma CO PIPELINE

#pragma CO SET stageDelay 32

findex -= SIN_X[k];

/*floor is the array index. Keeping just the integer bits of findex.*/

floor = findex>>8;

/*interpolation factor is the lower 16 bits of findex*/

itp factor2 = findex;

itp_factor1 = 1 - if2;

/*Interpolation between parallel projections. 32 bit result*/

temp = itp_factor1*sinorow[floor] + itp_factor2*sinorow[floor+1];

/*Drop 16 lower bits. Accumulate image pixel.*/

im_val[im_index++] = temp>>16;

}

findex_v += COS_Y[k];

findex = findex_cached;

```

#### Figure 3.8 Pipelining the backprojection code

Impulse C Stage Master Explorer provides graphical views of the pipeline generated from the code. The block summary displays the latency, the maximum stage delay, and the achieved rate of the pipeline. Stage Master has a source code view showing which statements in the code were grouped into a stage. The statements are annotated with numbers to show to which stage they belong. Figure 3.9 shows the source code view generated by Stage Master from the code in figure 3.8.

Figure 3.9 Impulse C Stage Master Explorer

The inner loop operation executes 512<sup>2</sup> times, and so the latency of the pipeline is irrelevant. Our goal is to achieve a rate of 1 while keeping the stage delay as low as possible to maximize the frequency of operation. One of the restrictions imposed by the Impulse C platform support package for the XD1000 was that the user logic had to be clocked at 100MHz. This made it even more crucial to keep the stage delay as low as possible. The stage delay is calculated as the sum of the unit delays of the individual operations in a stage. Bitwise operations, such as shifts, have a stage delay of 1. Arithmetic operations have a stage delay equal to the bit-width of the widest operand. In our pipeline, the interpolation step has the longest stage delay of 32 because a 32-bit result is generated in that step. Considering that we have a delay of at least 32, the idea is to try to divide the stages such that each stage has a delay of no more than 32. Hence we use the CO SET pragma to constrain the stage delay to 32, as seen in figure 3.6.

Once the stage delay is determined, we try to achieve a rate of 1 so that the pipeline is accepting inputs and producing results every cycle. However, the pipeline could only achieve a rate of 2 as seen in figure 3.7. Operations within a stage do not have dependencies and so do not affect the rate. The message "Multiple access to sinorow reduces minimum rate to 2" in Stage Master Explorer provides insight about the issue affecting the rate. In the interpolation step, we need to read 2 values form the array sinorow in the same cycle. This makes the rate 2 because only one value can be read from the memory at a time.

There are some ways to work around this and achieve the desired rate of 1. The first is to maintain two memories with the same values - sinorow1 and sinorow2. These two distinct memories can be accessed in the same cycle. The disadvantage of this method is that it doubles the memory required to implement the pipeline. As mentioned earlier, when the loop is unrolled, any increase in the resources required to perform the inner loop computation implies a very large increase in the overall design. Memories were a resource bottleneck in our design and so this was not a viable solution. A more efficient method is to implement sinorow as a true dual port memory. This enables reading two values from the memory at the same time. The Stratix II M4k RAM block is capable of implementing true dual port. In Impulse C, an array can be explicitly implemented using a particular memory type using the co\_array\_config() function. The declaration of the array is followed by the configuration statement designating it as true dual port

co\_int16 sinorow[SINO\_SIZE]; co\_array\_config(sinorow, co\_kind, "dualsync");

However, the Impulse C compiler does not allow memories accessed in more than one process to be explicitly configured. All operations with a particular memory (that needs explicit configuration) should be performed within the process that declares it. However, in our application we chose to keep the memory read operations in a separate process and the compute operations in another. Though we had initially conceived this partitioning simply as a logical way to break up the tasks to be performed, we found that it had implications for the ability of the synthesized design to meet the timing constraints. When we attempted to perform the memory read operations in the same process as the compute, the design would fail timing. We believe that the partitioning might have helped improve the placement of the design, thus enabling it to meet timing. Hence we decided to keep the memories in the default configuration and maintain the partitioning.

## 3.3. Design Architecture

The inner loop of the computation represents the task carried out by a single complete data path in the design. The optimization strategy is to create the most efficient hardware implementation of the inner loop possible and then replicate it as many times as the resources on the chip will allow. The previous section discussed all the optimization made to the inner loop. We now discuss replication of the data path and then present a system-level view of how the entire design operates.

## 3.3.1. Parallel Design Architecture

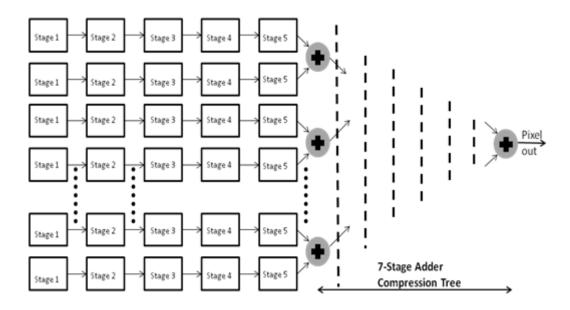

The loops in figure 3.8 find the contribution to every image pixel from one projection. If we replicate the computation inside the inner loop, we can simultaneously find the contribution to every image pixel from multiple projections. Based on resource availability, we decided to build a 128-way parallel system.

# 3.3.1.1. Loop Unrolling

The process of replicating the inner loop computation was achieved by manually unrolling the computation by duplicating each statement inside the compute loop 128 times with different variable names. Some of the statements could have been more elegantly unrolled using the CO Unroll pragma. However, the memory access patterns inside the inner loop require the compiler to infer that memories need to be broken into smaller distributed units, which the current version of the Impulse C tools is not capable of doing. This computation was simple enough that the manual unrolling process was not too painstaking, and was achieved rather easily using a standard text editor.