# Ultra Fast Transformers on FPGAs for Particle Physics Experiments

Anonymous Author(s) Affiliation Address email

## Abstract

| 1  | This work introduces a highly efficient implementation of the transformer architec-  |

|----|--------------------------------------------------------------------------------------|

| 2  | ture on a Field-Programmable Gate Array (FPGA) by using the hls4ml tool. Given       |

| 3  | the demonstrated effectiveness of transformer models in addressing a wide range of   |

| 4  | problems, their application in experimental triggers within particle physics becomes |

| 5  | a subject of significant interest. In this work, we have implemented critical com-   |

| 6  | ponents of a transformer model, such as multi-head attention and softmax layers.     |

| 7  | To evaluate the effectiveness of our implementation, we have focused on a particle   |

| 8  | physics jet flavor tagging problem, employing a public dataset. We recorded latency  |

| 9  | under 2 $\mu$ s on the Xilinx UltraScale+ FPGA, which is compatible with hardware    |

| 10 | trigger requirements at the CERN Large Hadron Collider experiments.                  |

|    |                                                                                      |

## 11 1 Introduction

Accelerated Machine Learning (ML) inference is necessary to run the algorithms in the online event 12 selection systems of the particle physics experiments. Due to the extremely high particle collision 13 frequency of 40 MHz at the Large Hadron Collider (LHC) [1] at CERN [2], it is impossible to read 14 out and store all the collision events. As a result, the LHC experiments [3, 4, 5, 6], try to read out only 15 the interesting via an online selection system called the trigger. Most of the LHC experiments use a 16 two-stage trigger system, hardware-based Level-1 trigger and software-based High-Level trigger. The 17 Level-1 trigger operates at 40 MHz, so the algorithms usually run on application-specific integrated 18 circuits (ASICs) or FPGAs. As the average number of collisions at the LHC is expected to increase 19 with time, sophisticated ML algorithms will be crucial for Level-1 triggers to efficiently filter events. 20 There have been numerous efforts to port ML algorithms like Deep Neural Networks [7], Convolution 21 Neural Networks [8], Recursive Neural Networks [9, 10], Graph Neural Networks [11] onto FPGAs 22 for physics applications using High-Level Synthesis (HLS) languages with the hls4ml package 23 [7, 12]. hls4ml is an HLS-based compiler for a neural network to FPGA firmware conversion. 24 In recent years, the transformer [13] architecture became popular for their great performance in 25

language modeling tasks like encoder-only BERT [14], decoder-only GPT [15], etc. Over time, the 26 utility of transformer models extended beyond language modeling, impacting a wide range of ML 27 applications. They are now widely used in particle physics for offline computing tasks like particle 28 reconstruction [16], identification [17, 18, 19], etc. Often the transformer-based models show better 29 performance over other architecture, but they are very computing intensive and suffer from a slow 30 inference rate. Because of the computationally intensive nature, it becomes challenging to implement 31 [20, 21, 22, 23] them on hardware like FPGAs, where a limited amount of resources is available. 32 Another previous work [24] explored this design space in the context of a particle physics experiment 33 by studying a small transformer for jet classification. 34

In this work, we present a flexible and efficient implementation of transformers written in HLS for the hls4ml package. This integration into hls4ml opens the door for wider low-latency applications of

Submitted to 37th Conference on Neural Information Processing Systems (NeurIPS 2023). Do not distribute.

<sup>37</sup> the Transformer models. Here the main focus is on the trigger applications in the LHC experiments.

<sup>38</sup> However, our implementation is very general and it is relevant to many real-time detector systems

<sup>39</sup> across fundamental science where low-latency high throughput inference is necessary.

## 40 **2** Benchmark study

To benchmark our implementations, we study the open data samples from the Compact Muon 41 42 Solenoid (CMS) experiment which contain top quark pairs decaying hadronically with center-of-mass energy of 7 TeV [25]. These events contain many bottom quark jets (b jets), charm quark jets (c 43 jets) and jets from light quarks, and gluons (light jets) originating from top quark decay. The jets 44 in the dataset are labeled as b, c, and light jets depending on whether they contain bottom quarks, 45 charm quarks, or neither, respectively. The main feature that separates b jets (and c jets) from light 46 47 jets is the presence of the displaced vertex corresponding to the decay of the hadron containing the b 48 (or c) quark. These hadrons are long-lived due to their mass, and the decay time depends on their 49 momenta. Our proposed algorithm aims to identify the presence of tracks that are consistent with these displaced vertices using a transformer architecture. 50

All the jets are reconstructed using the anti-kt algorithm with a distance parameter of R = 0.5. The 51 52 jets are required to have transverse momenta  $(p_T)$  larger than 30 GeV and absolute pseudorapidities less than 2.0. Charged particle tracks with  $p_{\rm T}$  larger than 1 GeV are associated with the nearest jet 53 if they are within the angular distance  $\Delta R$  (track, jet) of 0.5. Tracks within a jet are ordered by the 54 significance of their transverse impact parameter ( $S(d_0)$ ), and only the first 15 tracks are used for 55 this study. Each track is represented by a vector of six features: transverse and longitudinal impact 56 parameters  $(d_0, d_z)$  and their significances  $(\mathcal{S}(d_0), \mathcal{S}(d_z)), \Delta R(\text{track}, \text{jet})$ , and relative transverse 57 momentum between the track and the jet  $(p_{\rm T}({\rm track})/p_{\rm T}({\rm jet}))$ . 58

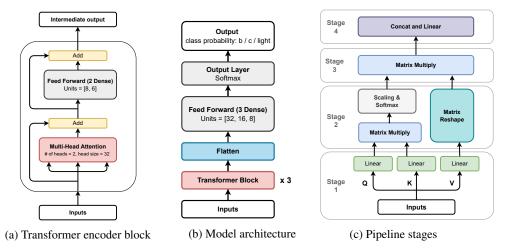

The flavor tagging classifier model is constructed using Keras+TensorFlow, using a transformer 59 architecture with 9135 trainable parameters. The padded sequence of tracks, with a maximum length 60 of 15, is directly fed into a transformer encoder block. No positional encoding is used, as the ordering 61 is not crucial for this problem. Each encoder block contains a multi-head attention (MHA) layer with 62 two heads, running two scaled dot-product attention layers in parallel, and a feed forward network 63 with two dense layers. Outputs of the MHA layer are passed through a feed forward block where 64 the layer dimensions are 8 and 6, respectively. Due to the simplicity of the flavour tagging problem, 65 we did not include a layer normalization after the MHA layer. The structure of the encoder block is 66 shown in Fig. 1a. The outputs of the encoder blocks are flattened and passed through three dense 67 layers with 32, 16, and 8 units. The output layer uses a softmax function and predicts three class 68 probabilities corresponding to b, c, and light jets. The model contains three encoder blocks and the 69 architecture is shown in Fig. 1b. The training is performed with a categorical cross-entropy loss, with 70 30% of the training data retained for validation and testing. 71

## 72 **3 Implementations**

One of the main focuses of this work is to implement the MHA layer in HLS. The implementation

of the MHA layer is divided into four sequential pipeline stages shown in Fig. 1c. Each stage is

explained below.

<sup>76</sup> The first stage is the Linear projection step where the inputs are transformed into Query (Q), Key

77 (K), and Value (V) vectors using separate weight matrices. A matrix times a vector operation is

<sup>78</sup> performed at each time step as a pipeline. To optimize FPGA resources, the vectors from this stage

are stored in a First In, First Out (FIFO) memory structure. This aligns perfectly with our sequential

data processing, ensuring efficient memory utilization and fostering an effective data flow for the

subsequent stages. Multiple FIFO memories are stacked together to increase the bandwidth.

The second stage starts computing the attention mechanism by taking the dot product of the Q and K vectors, producing a relevance score for each element of the input sequence. This score determines how elements influence each other in the sequence. The product is then divided by the dimension of the key vectors,  $\sqrt{d_k}$ , before passing it through a lookup table-based softmax function. The softmax output is stored in FIFO memory. Simultaneously, the matrix V is reshaped into a fully accessible array for later stages. 88 The third stage involves the matrix multiplication of the scores matrix and the corresponding V

<sup>89</sup> vectors. The V vectors are stored in a fully accessible register for the parallel multiplication process.

<sup>90</sup> The results are stored back in the FIFO memory and passed to the next stage of processing.

91 The fourth stage includes two key processes: the concatenation of the output from all attention heads

<sup>92</sup> and the subsequent linear transformation of the concatenated result. Each attention head provides an

output vector loaded row by row, aligning with the temporal sequencing of the data. Once loaded,

the outputs are concatenated together to form a single, unified data stream. Then the data stream is

passed through a linear layer. The linear layer is also pipelined, and it inputs and outputs one row of

<sup>96</sup> data at a time. This stage manages the output from all heads and efficiently generates the final output.

Figure 1: The encoder block used for the transformer model is shown in (a). The full model architecture is shown in (b). The pipeline stages for the multi-head attention layer is shown in (c).

Apart from implementing the MHA layer, we have also optimized the softmax HLS implementation

inside the hls4ml tool to reduce the computational cost. Softmax is used many times in the model,

<sup>99</sup> so it is crucial to have an efficient HLS implementation to run inference on an FPGA.

#### 100 4 Results

The flavour tagging model described in Sec. 2 is translated into an HLS model using the hls4ml framework. Our tests were done using Vivado HLS 2020.1 with a Xilinx UltraScale+ FPGA VU13P (part number xcvu13p-fhga2104-2L-e) as the target device. For the HLS implementation two different optimizations are studied: quantization and parallelization.

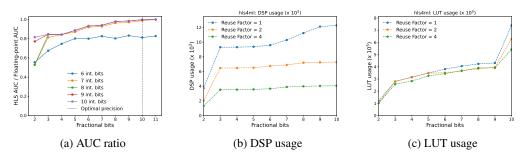

The quantization process reduces the numerical precision of the model parameters, such as weights 105 and biases, as well as inputs. Typically, ML model parameters are stored as 32-bit floating-point 106 numbers Although floating-point numbers offer an extensive dynamic range, they consume significant 107 computing resources when implemented on an FPGA. Therefore, for FPGA implementation, fixed-108 point numbers with fixed precision are preferred. This shift to fixed-point representation greatly 109 accelerates computation by reducing both computational resource usage and memory utilization. In 110 our study, we systematically explore fractional bit variations while maintaining a fixed precision of 6, 111 7, 8, 9, or 10 bits for the integer part. We evaluate the receiver operating characteristic (ROC) curve 112 for the transformer-based classifier employing the area under the curve (AUC) as a performance 113 metric. The ratio of the AUCs (fixed-point HLS model / floating-point Keras model) is shown in Fig. 114 2a as a function of fraction bits for integer bits. From the figure, it is clear that we need at least 10 115 integer bits and 10 fractional bits to get a similar performance as the floating-point model. 116

The hls4ml offers a valuable feature known as the "reuse factor" parameter, which plays a pivotal role

in governing the optimization of parallelization and the efficient utilization of computing resources.

This factor determines the number of times each multiplier is used for computing the neuron values

within a given layer. If the reuse factor is set to 1, the computation becomes fully parallel, as each

multiplication operation is executed independently by a dedicated digital signal processing (DSP) 121 block. As we increase the reuse factor the computing resource utilization decreases, but the latency 122 increases proportionally. To study the resource-latency trade-off and find an optimal implementation 123 for our model, we have synthesized (full Vivado synthesis) it with varying values of the reuse factor 124 and fractional bit precision. For each case, we quantified the utilization of FPGA resources of different 125 categories like memory (BRAM), DSPs, flip-flops (FFs), and lookup tables (LUTs). The utilization 126 of DSPs and LUTs are shown in Fig. 2b and Fig. 2c, respectively, as a function of fractional bits 127 (integer bit = 10) for reuse factors of 1, 2, or 4. As anticipated, the resource utilization goes up as we 128 reduce the reuse factor. It's worth noting that the target board has a total of 12288 DSPs and 1.72 129 million LUTs, providing us with flexibility in selecting any of the three reuse factors to achieve the 130 optimal precision of (int. = 10, frac. = 10) during the model synthesis. 131

Remarkably, the observed latency aligns with the requirements of the LHC hardware trigger. For the fully parallel scenario with a reuse factor 1, the model's inference latency is 2.077  $\mu s$ . Here, the clock period is 6.58 ns, resulting in output generation every 49 clock cycles or 322.42 ns. However, the latency increases to 3.467  $\mu s$  and 5.853  $\mu s$  for reuse factors of 2 and 4, respectively.

Figure 2: (a) Ratios of the fixed-point and floating-point AUCs as function of fractional bits. Five different values between 6 and 10 bits are chosen for the integer precision. Utilization of (b) DSP and (c) Lookup tables are shown as a function of fractional bits while keeping the integer part fixed to 10. Three different configurations with reuse factor of 1 (blue), 2 (orange), or 4 (green) are shown. The target board (part number xcvu13p-fhga2104-2L-e) has a total of 12288 DSPs and 1.72 million LUTs.

## **136 5 Summary and Outlook**

We have successfully implemented a transformer architecture with multi-head attention in HLS 137 for FPGA inference. This implementation has been seamlessly incorporated into the hls4ml pack-138 age, which facilitates the automatic translation of transformer models for low-latency inference 139 applications. It is essential to note that some critical features, including positional encoding and 140 layer normalization, have been left for future work. To demonstrate the effectiveness of the current 141 implementation, we conducted a study using a flavor tagging model. Notably, the model's inference 142 latency falls within a range of 2 to 6  $\mu s$ , fully complying with the stringent timing constraints of the 143 hardware triggers. What sets our implementation apart is its exceptional versatility. It can readily 144 adapt to models with different configurations, such as varying sequence lengths and the number of 145 attention heads, without the need for extensive customization. As a result, this integration represents 146 a pivotal development, and paves the way for the widespread utilization of low-latency applications 147 employing transformer models. 148

## **149 6 Broader Impact**

Although we demonstrate the performance of one specific algorithm here, this work could be used to accelerate other reconstruction algorithms in particle physics experiments. In fact, hls4ml transformer can be used for low latency inference for other scientific domains like neuroscience, gravitational wave, material science, etc., and various non-scientific domains.

## 154 References

- [1] Lyndon Evans and Philip Bryant. LHC machine. JINST, 3(08):S08001–S08001, aug 2008.

- [2] Cern accelerating science. (n.d.). https://home.cern/science/accelerators/

large-hadron-collider, 2016.

- [3] ATLAS Collaboration. The atlas experiment at the cern large hadron collider. *JINST*, 3:S08003, 2008.

- [4] ALICE Collaboration. The ALICE experiment at the CERN LHC. *JINST*, 3(08):S08002–

S08002, aug 2008.

- [5] CMS Collaboration. The CMS experiment at the CERN LHC. *JINST*, 3(08):S08004–S08004,

aug 2008.

- [6] LHCb Collaboration. The LHCb detector at the LHC. *JINST*, 3(08):S08005–S08005, aug 2008.

- [7] J. Duarte, S. Han, P. Harris, S. Jindariani, E. Kreinar, B. Kreis, J. Ngadiuba, M. Pierini, R. Rivera,

N. Tran, and Z. Wu. Fast inference of deep neural networks in fpgas for particle physics. *Journal of Instrumentation*, 13(07):P07027, jul 2018.

- [8] Thea Aarrestad, Vladimir Loncar, Nicolò Ghielmetti, Maurizio Pierini, Sioni Summers, Jennifer

Ngadiuba, Christoffer Petersson, Hampus Linander, Yutaro Iiyama, Giuseppe Di Guglielmo,

Javier Duarte, Philip Harris, Dylan Rankin, Sergo Jindariani, Kevin Pedro, Nhan Tran, Mia Liu,

Edward Kreinar, Zhenbin Wu, and Duc Hoang. Fast convolutional neural networks on fpgas

with hls4ml. *Machine Learning: Science and Technology*, 2(4):045015, jul 2021.

- [9] Elham E. Khoda et al. Ultra-low latency recurrent neural network inference on FPGAs for physics applications with hls4ml. *Mach. Learn. Sci. Tech.*, 4(2):025004, 2023.

- [10] Zhiqiang Que et al. Accelerating Recurrent Neural Networks for Gravitational Wave Experiments. In *32nd IEEE International Conference on Application-specific Systems, Architectures and Processors*, 6 2021.

- [11] Abdelrahman Elabd et al. Graph Neural Networks for Charged Particle Tracking on FPGAs.

*Front. Big Data*, 5:828666, 2022.

- [12] Farah Fahim et al. hls4ml: An Open-Source Codesign Workflow to Empower Scientific

Low-Power Machine Learning Devices. In *tinyML Research Symposium 2021*, 3 2021.

- [13] Ashish Vaswani, Noam Shazeer, Niki Parmar, Jakob Uszkoreit, Llion Jones, Aidan N. Gomez,

Lukasz Kaiser, and Illia Polosukhin. Attention is all you need, 2023.

- [14] Jacob Devlin, Ming-Wei Chang, Kenton Lee, and Kristina Toutanova. Bert: Pre-training of

deep bidirectional transformers for language understanding, 2019.

- [15] Alec Radford, Karthik Narasimhan, Tim Salimans, Ilya Sutskever, et al. Improving language

understanding by generative pre-training. 2018.

- [16] Alexander Shmakov, Michael James Fenton, Ta-Wei Ho, Shih-Chieh Hsu, Daniel Whiteson,

and Pierre Baldi. SPANet: Generalized permutationless set assignment for particle physics

using symmetry preserving attention. *SciPost Phys.*, 12(5):178, 2022.

- <sup>191</sup> [17] Huilin Qu, Congqiao Li, and Sitian Qian. Particle Transformer for Jet Tagging. 2 2022.

- [18] V. Mikuni and F. Canelli. Abcnet: an attention-based method for particle tagging. *The European Physical Journal Plus*, 135(6):463, 2020.

- [19] Vinicius Mikuni and Florencia Canelli. Point cloud transformers applied to collider physics.

*Machine Learning: Science and Technology*, 2(3):035027, jul 2021.

- [20] Bingbing Li, Santosh Pandey, Haowen Fang, Yanjun Lyv, Ji Li, Jieyang Chen, Mimi Xie, Lipeng

Wan, Hang Liu, and Caiwen Ding. Ftrans: Energy-efficient acceleration of transformers using

fpga, 2020.

- [21] Hongwu Peng, Shaoyi Huang, Tong Geng, Ang Li, Weiwen Jiang, Hang Liu, Shusen Wang, and Caiwen Ding. Accelerating transformer-based deep learning models on fpgas using column balanced block pruning. In 2021 22nd International Symposium on Quality Electronic Design (ISQED), pages 142–148, 2021.

- [22] Georgios Tzanos, Christoforos Kachris, and Dimitrios Soudris. Hardware acceleration of

transformer networks using fpgas. In 2022 Panhellenic Conference on Electronics Telecommu nications (PACET), pages 1–5, 2022.

- [23] Seongmin Hong, Seungjae Moon, Junsoo Kim, Sungjae Lee, Minsub Kim, Dongsoo Lee, and

Joo-Young Kim. Dfx: A low-latency multi-fpga appliance for accelerating transformer-based

text generation, 2022.

- [24] Filip Wojcicki, Zhiqiang Que, Alexander D Tapper, and Wayne Luk. Accelerating transformer

neural networks on fpgas for high energy physics experiments. In 2022 International Conference

on Field-Programmable Technology (ICFPT), pages 1–8, 2022.

- 212 [25] Mc: Ttbar sample from the cms hep tutorial. http://opendata.cern.ch/record/204.