# Software Technologies for Reconfigurable Systems

#### **Scott Hauck**

Department of ECE Northwestern University Evanston, IL 60208 USA hauck@ece.nwu.edu

#### **Anant Agarwal**

Department of EECS Massachusetts Institute of Technology Cambridge, MA 02139 USA agarwal@lcs.mit.edu

## Abstract

FPGA-based systems are a significant area of computing, providing a high-performance implementation substrate for many different applications. However, the key to harnessing their power for most domains is developing mapping tools for automatically transforming a circuit or algorithm into a configuration for the system. In this paper we review the current state-of-the-art in mapping tools for FPGA-based systems, including single-chip and multi-chip mapping algorithms for FPGAs, software support for reconfigurable computing, and tools for run-time reconfigurability. We also discuss the challenges for the future, pointing out where development is still needed to let reconfigurable systems achieve all of their promise.

## **1.0 Introduction**

Reconfigurable computing is becoming a powerful methodology for achieving high-performance implementations of many applications. By mapping applications into FPGA hardware resources, extremely efficient computations can be performed. In [Hauck98] we presented numerous reconfigurable systems, and described the varied roles of these systems. However, hardware is only one part of a complete system. In order for multi-FPGA systems to achieve widespread use, they not only require an efficient hardware implementation medium, but also a complete, automatic software flow to map circuits or algorithms onto the hardware substrate. Similar to a compiler for a standard programming language, the mapping software for a multi-FPGA system takes in a description of the circuit to be implemented, and through a series of transformations creates an implementation of the circuit in the basic primitives of the hardware system. In a multi-FPGA system, this implementation is programming files or bitstreams for the FPGAs in the system.

For the developers and users of reconfigurable systems there is a tradeoff to be made between hand mapping to the system, creating high-quality implementations but requiring a very hardware-savvy user, and automatic tools which free the user from some implementation details, but which can (sometimes substantially) impact the resulting quality. In this paper we focus primarily on software tools to partially or completely automate the mapping process. While these algorithms are still in their infancy, our hope is that they will lead to an efficient, automatic mapping solution for reconfigurable systems. However, it is important to realize that there will always be a role for hand-mapped implementations, just as in the compiler-dominated world of general-purpose computing there is still a role for assembly-language programming where the required quality demands the highest performance implementation possible.

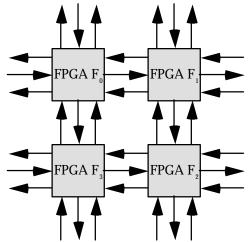

Before we discuss the specific steps necessary to map onto a multi-FPGA system, it is necessary to consider some of the features of a multi-FPGA system that impact this software flow. One of the most important concerns in multi-FPGA systems is that while the FPGAs are reprogrammable, the connections between the FPGAs are fixed by traces on the circuit board. Thus, not all FPGAs may be interconnected, and communication between FPGAs must be carried on these limited resources. If the source and destination of a route are on different FPGAs, and the FPGAs are not directly connected, this signal will need to traverse one or more intermediate FPGAs. This adds extra delay to the routing, and uses up multiple FPGA I/O pins. This latter constraint can be the major bottleneck in multi-FPGA systems, with I/O resource constraints in some cases (especially logic emulation) limiting achieved logic utilization of FPGAs to 10%-20%. Thus, the primary concern of mapping tools for a multi-FPGA system is limiting the amount of I/O resources needed by a mapping. Not only does this mean that most signals should be kept within a single FPGA, but also that those signals that need to be communicated between FPGAs should be communicated between neighboring FPGAs. Thus, the mapping tools need to understand the topology of the multi-FPGA system, and must optimize the mapping to fit within this routing topology. Note that some topologies

use crossbars or FPICs<sup>1</sup>, devices meant to ease this I/O bottleneck. However, even these chips have finite I/O resources, and the connections between them and the FPGAs are fixed. Thus the restrictions of a fixed topology occur even in these systems.

Not only must the tools optimize to a fixed topology, but in some circumstances they must also be fully automatic. In the case of logic emulation, the user of the system has no desire to learn all the details of a multi-FPGA system, and will be unwilling to hand-optimize their complex design to a multi-FPGA system. The system is meant to speed time-to-market of the system under validation, and without an automatic mapping solution the speed benefits of emulation will be swamped by the mapping time and human effort. Also, for a multi-FPGA system targeted to general software acceleration, the users of the system will be software programmers, not hardware designers. While there are situations where a hand-optimized solution may be the right answer, for many other domains a complete, automatic mapping system is a necessity. Merging these two demands together, developing an automatic system with the ability to also take user input to partially or completely guide the mapping process will be an important concern for reconfigurable systems.

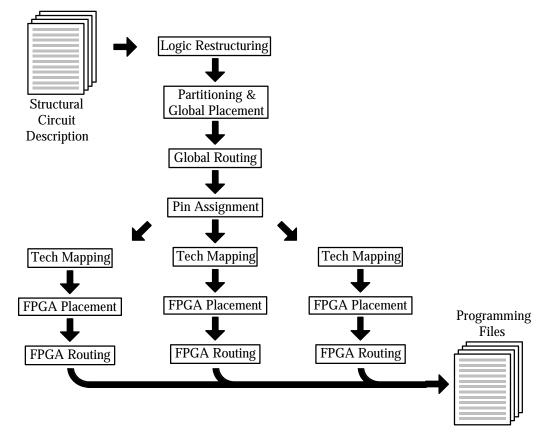

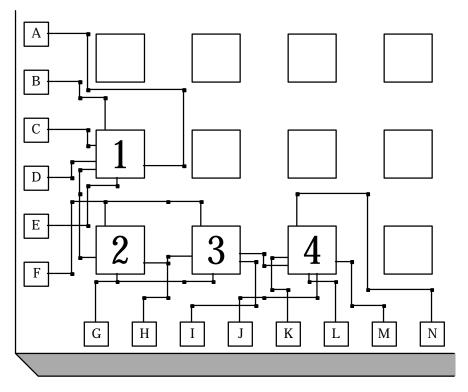

Figure 1. Multi-FPGA system mapping software flow.

The final major constraint is that the performance of the mapping system itself is an issue. A multi-FPGA system is ready to use seconds after the mapping has been developed, since all that is necessary is to download the FPGA configuration files to the system. Thus, the time to create the mapping dominates the setup time. If the mapping tools take hours or days to complete, it is difficult and time-consuming to make alterations and bug fixes to the mapping. This is especially important for rapid-prototyping systems, where the multi-FPGA system is part of an iterative process of bug detection, correction, and retesting. If the mapping time is excessive, the multi-FPGA

<sup>&</sup>lt;sup>1</sup> FPICs are reconfigurable, routing-only devices which can perform nearly arbitrary interconnctions between their inputs [Aptix93, I-Cube94].

system will be used relatively late in the design cycle (where bugs are few), which greatly limits their utility. With a mapping process that takes only minutes, it becomes possible to use the benefits of logic emulation much earlier in the design cycle, increasing the usefulness of a multi-FPGA system.

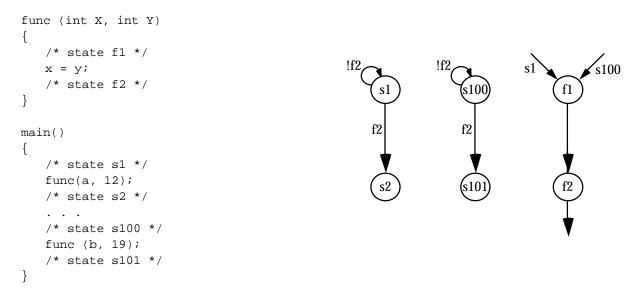

#### 2.0 Overview

The input to the multi-FPGA mapping software may be a description in a hardware description language such as Verilog or VHDL, a software programming language such as C or C++, or perhaps a structural circuit description. A structural circuit description is simply a representation of a circuit where all the logic is implemented in basic gates (ANDs, ORs, latches, etc.), or in specific, premade parts (i.e., microprocessors, memories, etc.). Programming language descriptions (Verilog, VHDL, C) differ from structural descriptions in that the logic may be described more abstractly, or "behaviorally", with the functions described by what needs to be done, not by how it should be implemented. Specifically, an addition operation in a behavioral description would simply say that two values are added together to form a third number, while a structural descriptions, there are automatic methods for converting such descriptions into structural circuit descriptions. Details of such transformations can be found elsewhere [McFarland90]. Our discussion of the mapping process starts with structural circuit descriptions, while sections 5 and 6 will overview methods for handling higher level specifications.

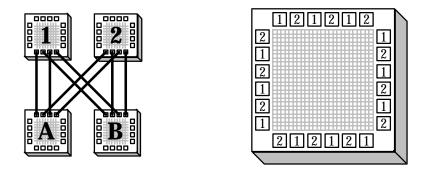

To convert from a structural circuit description to a multi-FPGA realization requires a series of mapping steps (Figure 1). These steps include logic restructuring, partitioning & global placement, global routing, pin assignment, and FPGA technology mapping, placement and routing. FPGA technology mapping, placement and routing are identical to the tools used for single FPGAs. In the pages that follow, we will first give a brief overview of the process. A more in-depth discussion of each of the steps appears later in this paper.

The first mapping step is logic restructuring. Logic restructuring alters the input netlist so that it can be mapped to the multi-FPGA system. Asynchronous components and gated clocks may need to be carefully considered or isolated, and RAM usage must be made to fit into the physical RAM chips available in the system.

After logic restructuring, partitioning takes the single input circuit description and splits it into pieces small enough to fit into the individual FPGAs in the system. The partitioner must ensure not only that the partitions it creates are small enough to fit the logic capacity of the FPGAs, but must also ensure that the inter-FPGA routing can be handled within the constraints of the multi-FPGA routing topology. Commonly global placement, the process of assigning partitions to specific FPGAs in the system, is combined with the partitioning stage. Otherwise, it is unclear where a given partition resides within the multi-FPGA topology, and thus it can be difficult to properly optimize the interpartition connectivity.

After partitioning and global placement, global routing handles the routing of inter-FPGA signals (i.e., the signals that need to be communicated between partitions). This phase can be broken up into abstract global routing and detailed global routing (pin assignment). Abstract global routing (hereafter referred to simply as global routing) determines through which FPGAs an inter-FPGA signal will be routed. Pin assignment then decides which specific I/O pins on each of the FPGAs will carry the inter-FPGA signals.

Once partitioning, global placement, global routing, and pin assignment are completed, all that is left is the technology mapping, placement and routing of the individual FPGAs in the system. When these steps are completed, there will be configuration files prepared for each FPGA in the system. Downloading these files to the multi-FPGA system then customizes the multi-FPGA system, creating a complete realization of the desired functionality.

In the sections that follow, we will discuss techniques for implementing each of these operations. Section 3 covers single-chip mapping tools, reviewing techniques from standard FPGAs for use in reconfigurable systems. Then, section 4 discusses multi-chip tools, showing what techniques are necessary to convert the multi-FPGA mapping problem into a set of independent single-chip mappings. Finally, we consider tools and techniques specialized for FPGA-based computation, including reconfigurable computing techniques in section 5, and run-time

reconfigurability in section 6. We then sum up the paper, providing an overview of current systems, as well as a description of areas for future innovation.

#### 3.0 Single-Chip Mapping Tools

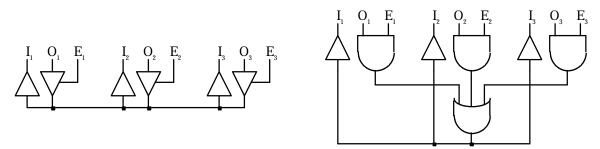

While some circuits are designed by hand, in many cases automatic mapping software is critical to logic development. This is particularly true for technologies such as FPGAs, where in general the complete mapping process is carried out by mapping software. In the following sections we will discuss some of the most important steps in mapping to LUT (lookup-table) based FPGAs. Note that the process is similar, but not identical, for other types of FPGAs. First is technology mapping, which restructures the input netlist into the logic blocks of the FPGA. Next, placement decides which specific logic blocks inside the FPGA will contain the logic functions created by technology mapping. Finally, routing determines what routing resources inside the FPGA will be used to carry the signal from where they are generated to where they are used. A more detailed treatment of all of these tasks can be found elsewhere [Venkateswaran94]. These single-chip FPGA mapping tools provide a method for implementing arbitrary logic within an FPGA, and form an important part of all mapping methodologies for FPGA-based systems.

#### 3.1 Technology Mapping

The user of an FPGA provides as input a circuit specified as some interconnection of basic logic gates and functions. These functions may have more or less inputs than the LUTs in the FPGA that will implement them. When the logic gate has too many inputs, it must be split into smaller functions which can fit inside the LUTs in the FPGA. If the gates have too few inputs, several interconnected gates could be combined to fit into a single LUT, decreasing the amount of LUTs needed to handle the mapping. By reducing the number of LUTs, more logic can be fit in the same sized FPGA, or a smaller FPGA could be used. The process of restructuring the logic to best fit the logic blocks in an FPGA is called technology mapping.

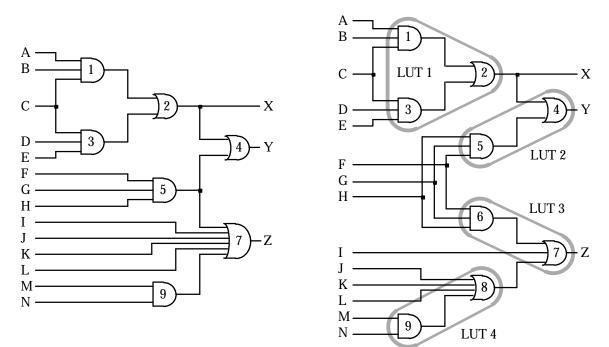

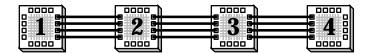

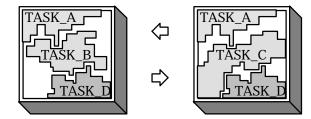

**Figure 2.** Example of 5-input LUT technology mapping. The input circuit (left) is restructured and grouped together into 5-input functions (right). The gray loops at right indicate individual LUTs. The numbers on the gates are for identification.

There are many different methods and approaches to the technology mapping of circuits for FPGA implementation [Brown92a, Vincentelli93]. An example of this process is shown in Figure 2. The circuit at left is restructured

into four 5-input LUTs, designated by the gray loops at right. Some of the logic functions, such as gate 7 at left, have more inputs than the LUT can handle. Thus, the gate will be split ("decomposed") into two gates (7 and 8 at right). Then, the gates are grouped together ("covered") into LUTs, while trying to minimize the total number of LUTs required. Note that this grouping can be complex. For example, even though gates 1 and 3 each have three inputs, and thus should not fit into a single LUT with gate 2, since input C is shared between the two gates a single 5-input LUT can handle all three gates. Finding this reconvergent fanout can be difficult. Also, this grouping process can cause the logic to be restructured. For example, gate 5 at left is duplicated, creating gates 5 and 6 at right. Although this seems like it would increase the hardware cost, replicating the logic can actually reduce the logic cost. In the example shown, if gate 5 was not replicated, it could not be grouped with either of its fanouts, since by grouping a gate with its fanout the gate's output is no longer available to other functions. However, by duplicating the gate, the duplicates can each be grouped with one of the fanouts, reducing the total LUT count.

Many approaches and optimizations are possible for technology mapping. For example, Chang et al. [Chang96] provides an approach that is capable of optimizing either the number of lookup tables or the latency of the resulting circuit. Similarly, methods for area and speed optimization are found in [Abouzeid93]. Instead of just mapping for LUT count, some algorithms optimize for performance or routeability (i.e., how easy it is to route the logic generated by technology mapping). Also, real FPGAs usually have logic blocks that are more complex than a single n-input LUT, and thus require more complex mapping algorithms. Recognizing that the use of LUT-based function units and restricted interconnect requires non-traditional logic synthesis approaches, Hwang et al. [Hwang94] present a logic synthesis technique based on communication complexity analysis. Numerous approaches to these and other mapping issues are presented in the literature, including work on logic decomposition [Murgai94, Chen95, Huang95a, Sawada95, Shen95, Stanion95, Wurth95, Leg196], covering [Cong92, Cong93, Farrahi94], and combined approaches [Francis90, Murgai90, Francis91a, Francis91b, Murgai91a, Murgai91b].

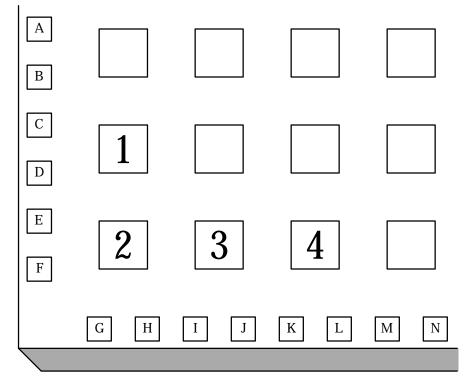

**Figure 3.** Placement of the circuit from Figure 2. The numbers are the number of the LUT (from the technology mapping) assigned to each logic block, while the letters are the assignment of input signals to I/O blocks.

Technology mapping can fit at several points within a complete multi-chip mapping system. As one example technology mapping can be performed after all multi-chip mapping steps (partitioning, global routing, and pin assignment) are completed. This allows the technology-mapping of the FPGAs to be performed in parallel (perhaps distributed across a set of workstations), speeding up the mapping process. However, if a circuit is partitioned before it is technology mapped, the partitioner must rely on estimates of circuit and component sizes, perhaps introducing inaccuracy into the mapping process. Recent work [Hauck95a] demonstrates that this inaccuracy is more than made up for by the added flexibility that pre-technology mapping partitioning can exploit, and thus we believe that technology mapping should in fact be performed only after all multi-chip mapping steps are completed.

#### 3.2 Placement

Placement takes the logic functions formed by technology mapping and assigns them to specific logic blocks in the FPGA. This process can have a large impact on the capacity and performance of the FPGA. Specifically, routing between distant points in an FPGA requires a significant amount of routing resources. Thus, this path will be much slower, and use up many valuable resources. Because of this, the primary goal of placement is to minimize the length of signal wires in the FPGA. To do this, logic blocks that communicate with one another are placed as close together as possible. For example, Figure 3 shows a placement of the logic functions created by technology mapping in Figure 2. Since function 2 takes the output of function 1 as an input, and shares inputs F, G, and H with function 3, function 2 is placed between function 1 and function 3. Also, F, G, and H are assigned to I/O blocks close to function 2.

Placement is a complex balancing act. Logic circuits tend to have a significant amount of connectivity, with many different functions communicating together. Trying to find the best two-dimensional layout of these elements can be quite difficult, since many functions may want to be placed together to minimize communications, while only a small fraction will fit within a given region of the FPGA. Thus, the placement tool must decide which functions are most important to place together, not just to minimize the distances of communications between these functions, but to minimize the total communication in the system.

The most common technique for performing placement for FPGAs (as well as other technologies) is simulated annealing [Shahookar91]. In order to use simulated annealing to solve an optimization problem, the programmer must generate a cost function and a move function. A cost function looks at a state of the system and assigns a value to the desirability of that state, with a lower value indicating a better result. For placement, a state of the system would be an assignment of logic functions to logic blocks, and I/O connections to I/O blocks. A cost function could be the total wirelength necessary to route in this configuration. Estimates are often used, since exact numbers are time-consuming to calculate, and simulated annealing requires the cost metric to be quickly computed. Alternatively, exact costs can be used if incremental costs can be quickly computed for a given move. Thus, states that have the smallest cost would require the least amount of routing, and would be better placements. More complex cost metrics, which take into account issues such as critical paths, are also possible. A move function is simply a method of transforming the current state of the system into a new state. Through repeated applications, this function should be capable of transforming any state of the system to any other. For placement, a move function could be to randomly pick two logic blocks in the FPGA and swap their contents.

One way to perform placement once a cost and move function are defined is to first pick a random starting point. The algorithm then repeatedly applies the move function to the current state of the system, generating a new state. If this state has a lower cost than the current state, it is accepted, and replaces the current state. Otherwise the current state is retained. Thus, this algorithm will greedily accept good moves, and move into a local minimum in the cost function's state space. The problem is that most cost functions have a huge number of local minima, many of which are much worse than the optimal placement (Figure 4). Specifically, from a given state there may be no way to swap two logic functions and reduce the cost (thus, we are in a local minima), though two or more pairs of swaps can greatly improve the placement.

Simulated annealing avoids the problem of getting caught in local minima. Like the greedy algorithm, simulated annealing takes the current state, uses the move function to generate a new state, and compares the cost metric in both states. If the move is a good move (that is, the cost function is lower for the new state than the old state) the

new state replaces the current state. However, instead of rejecting all bad moves (moves that increase the cost function), simulated annealing accepts some bad moves as well. In this way, the algorithm can get out of a local minima by accepting one or two bad moves. Subsequent good moves will then improve the results again, hopefully finding better results than the previous local minima.

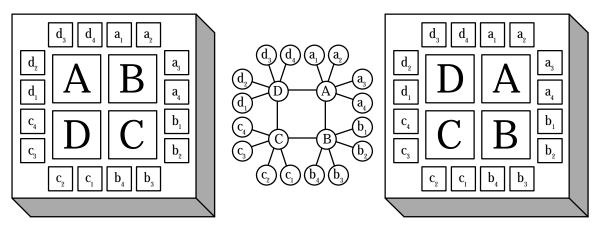

**Figure 4.** An example of a local minima in placement. The circuit at center, placed as shown at left, is in a local minima. No swap of logic or I/O functions will reduce the total wirelength. However, the placement at right is significantly better.

The method of how to determine what bad moves to accept is critical. The probability of accepting a bad move is usually  $\exp(-\Delta CT)$ , where  $\Delta C$  is the difference between the current and the new state's cost functions, and T is the temperature, a parameter that allows more or less bad moves to be accepted. Whenever the algorithm finds a bad move, it calculates the different between the current and new state. The algorithm then randomly determines whether to accept this bad move, and it is more likely to accept moves causing small increases in the cost function than big increases in the cost function (that is, the worse the move, the less likely it is to be accepted). Also, over time it gets pickier, accepting less and less bad moves. This is done by lowering the temperature parameter T. At the beginning of the annealing the algorithm accepts many bad moves, and randomly wanders around the search space. Since it always accepts good moves, it tends to stay in the portion of the search space where better states are found, but the large amount of bad moves accepted keep it from getting stuck in any one place. As time goes on, Tis decreased, and the algorithm accepts less and less bad moves. As this happens, it gets harder for the algorithm to wander away from the areas in the cost function where the better states are found. Thus, it is stuck in one region of the state space based on very coarse-grain measures of goodness, and it begins to stay in parts of this region where better states are found. The algorithm continues to accept less and less bad moves, until eventually it accepts only good moves. At this point, the algorithm is zeroing in on a local minima, though this minima tends to be much better than the average local minima in the search space, since the algorithm has slowly gravitated to areas in the search space where better states are found. In this way, simulated annealing can find much better results than greedy approaches in complex search spaces.

By applying simulated annealing to a placement problem, the complex relationships between the logic in the mapping can be considered. The algorithm will slowly optimize the state, coming up with a good final placement. Note that simulated annealing can be quite time-consuming. This is because the algorithm must be allowed to accept many good and bad moves at each acceptance level, so that the algorithm can explore much of the search space. Thus, multiple hour annealing runs are not unusual.

#### 3.3 Routing

Routing for FPGAs is the process of deciding exactly which routing resources will be used to carry signals from where they are generated to where they are used. Unlike many other technologies, FPGAs have prefabricated routing resources. Thus, instead of trying to limit the size of routing channels (the goal in standard cell routing), an FPGA router must work within the framework of the architecture's resources. Thus, the router must consider

the congestion of signals in a channel, making sure than no more routes are made through a region than there are resources to support them. Otherwise, if too many resources are required the routing fails, while in other technologies the region could just be enlarged.

An example of the routing of the placement from Figure 3 is shown in Figure 5. The router must decide which inputs and outputs of the logic blocks to connect to, which channels to route through, and how to connect through the switchboxes in the architecture. It is allowed to choose which terminal on the logic block to connect to because the logic is implemented in LUTs, and all inputs to a LUT are equivalent (assuming the programming of the LUT is modified accordingly). In deciding which channels and wires to use, and how to connect through the switchboxes, the router must ensure that there are enough resources to carry the signal in the chosen routing regions, as well as leaving enough resources to route the other signals in the system. One algorithm for performing this routing is presented in [Brown92b]. Here, the algorithm is divided into a global and a detailed router. The global router picks which routing regions the signal will move through. Thus, it will select the routing channels used to carry a signal, as well as the switchboxes it will move through. In this process, it takes care not to assign more signals to a channel than there are wires. However, the global router does not decide the wire assignment (i.e., which specific wires to use to carry each signal). The detailed router handles this problem, making sure that it finds a connected series of wires in the channels and switchboxes chosen by the global router that connects from the source to all the destinations. Both algorithms worry about congestion-avoidance, making sure that all signals can be successfully routed, as well as minimizing wirelength and capacitance on the path, attempting to optimize the performance of the circuit. By running both algorithms together, a complete routing solution can be created.

**Figure 5.** Routing of the placement from Figure 3. The small black squares are the configuration points used for this mapping.

Once the circuit has been technology mapped, placed, and routed, a complete implementation of the circuit on a given FPGA has been created. A simple post-processing step can now turn this implementation into a configuration file for the FPGA which can be downloaded to the reconfigurable system to implement the desired circuit. In the sections that follow we will describe how a large circuit design can be broken into multiple, single-chip mappings.

### 4.0 Multi-Chip Systems

FPGA vendors have provided tools that can take a mapping intended for a single FPGA, and automatically create a configuration file, and thus an FPGA-based realization of the design. However, many FPGA-based systems do not consist of simply a single FPGA, but may have multiple FPGAs connected together into a multi-FPGA system, as well as perhaps memory devices and other fixed resources. Mapping a circuit to such a system is much more complex than the single-chip mapping process, including considerations and constraints not found within a single FPGA. In this section we discuss techniques for solving these problems, presenting the current state-of-the-art in multi-FPGA mapping. These techniques, in conjunction with those described in the previous section, are capable of taking a complex circuit (one that is much larger than the capacity of a single FPGA) and create a complete implementation.

### 4.1 Software Assist for the Hand-Mapping Process

Perhaps the simplest method for mapping to a multi-FPGA system (at least from the tool developer's standpoint) is to have the user produce the mapping from scratch, specifying the complete implementation details. This requires the user to have a good understanding of their application and the reconfigurable system, but will potentially allow the user to create a much better implementation than is possible with an automatic mapping system.

Producing a mapping completely from scratch, with no software support, is often impossible. At a minimum, for most FPGAs it is necessary to rely on a software tool to create the bit patterns to load into the FPGA from a placed and routed circuit, since the information to do this by hand is often not provided by the FPGA vendors. However, there are several other ways in which software automation can help in even a hand-mapping environment. For example, when laying out a regular structure like an adder circuit, a user need not specify the exact location of each individual adder cell, and would much rather just state that the adder cells are placed next to one-another down a specific column in the FPGA. Also, a user may wish to create a specific hardware template for a commonly occurring component in their design and then replicate it as needed. Several such systems, which act as assistants to the hand-mapping process, and automate some of the less critical portions of the mapping process, have been produced [Gokhale95, Vuillemin96]. These systems remove some of the complexity of the hand-mapping process, allowing the designer to concentrate on the more important aspects of the design. However, these systems do not replace the designer, and require a user with a high degree of knowledge and sophistication. For less experienced users, or less demanding tasks, higher levels of automation are often essential.

In the rest of the paper we concentrate on the automation of the mapping process, attempting to develop a "compiler" for an FPGA-based system. However, with each of these systems it is important to realize that handmapping is often an alternative, and the quality losses due to software automation must be balanced against the design complexity of performing that optimization by hand. It is important to note that most high-performance systems based on FPGAs have largely been mapped to manually. Hopefully, in the decade to come we will transition to a model more in line with general-purpose computing, where most programs are translated from a high-level language into machine instructions via a completely automatic mapping process, though where there is still the potential for assembly-language programming (the hand-mapping of the software world) in situations where the performance gains are large enough or important enough to make such efforts worthwhile.

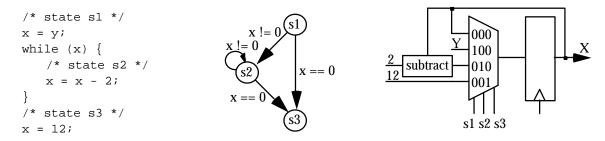

## 4.2 Partitioning and Global Placement

The user of a multi-FPGA system usually specifies the desired functionality as a single, large structural circuit. This circuit is almost always too large to fit into a single FPGA, and must instead be split into pieces small enough to fit into multiple FPGAs. When the design is split up, there will be some signals that need to be communicated between FPGAs because two or more logic elements connected to this signal reside on different FPGAs. This communication is a problem for a multi-FPGA system, because the amount of I/O resources on the FPGAs tends to be used up long before the logic resources are filled.

Because I/O resources are the main limitation on logic capacity in a multi-FPGA system, the primary goal of the partitioner, the tool that splits logic up into FPGA-sized partitions, is to minimize the communication between partitions. There have been many partitioning algorithms developed that have as a primary goal the reduction of

inter-partition communication, and which can split a design into multiple pieces, including algorithms designed specifically to map into multiple FPGAs [Kuznar93, Woo93, Kuznar94, Weinmann94, Chan95, Huang95b, Kuznar95, Fang96]. One such algorithm [Chou94] is also designed to efficiently handle the large circuits encountered during logic emulation. Instead of partitioning the entire circuit, it instead focuses only on a small portion of the circuit at a time. Although this speeds up the partitioning, it may cause the algorithm to ignore more global concerns, including assigning logic to more than one partition. To fix these problems, the algorithm uses an technique inspired by the ESPRESSO II logic minimization package [Brayton85] to recombine and restructure the partitioning. If logic is assigned to multiple partitions, the algorithm will restructure the partitions to remove the overlap. Also, more global concerns will be handled by breaking the partitions initially created into smaller portions and recombining them into (hopefully) a better final partitioning.

Unfortunately, many previous multiple-FPGA algorithms are not designed to work inside a fixed topology. Specifically, most multi-way partitioning algorithms, algorithms that break a mapping into more than 2 parts, assume that there is no restriction on which partitions communicate. They only seek to minimize the total amount of that communication, measured as either the total number of nets connecting logic in two or more partitions (the net-cut metric), or the total number of partitions touched by each of these cut nets (the pin-cut metric). These are reasonable goals for when the partitioner is run before the chips are interconnected, and is used in cases where someone is building a custom multi-FPGA system for a specific application. However, most multi-FPGA systems are prefabricated, with the FPGAs connected in a routing topology designed for general classes of circuits, and these connections cannot be changed. Thus, some FPGAs may be interconnected in the topology, while others will not, and the partitioner needs to understand that the cost of sending a signal between pairs of FPGAs depends on which FPGAs are communicating. Even when the multi-FPGA system is custom designed for an application, later modifications to the circuit will require similar, topology-aware partitioning tools.

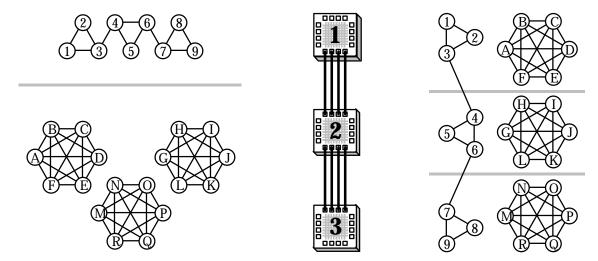

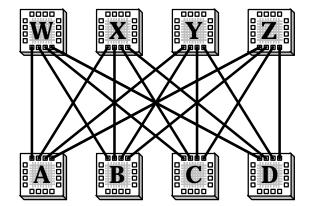

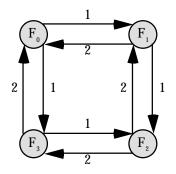

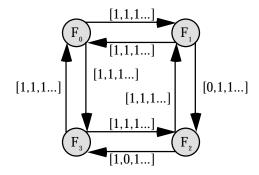

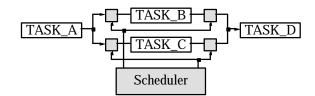

Figure 6. Example system for topological effects on multi-FPGA system partitioning.

For an example of topological issues in multi-FPGA system partitioning, consider a linear array of 4 FPGAs, numbered 1-4 (Figure 6). A signal communicated between FPGAs 1 & 2 will consume two I/Os, one on each FPGA, since the FPGAs are directly connected. A signal between FPGAs 1 & 4 will consume six I/Os, two between 1 & 2, two between 2 & 3, and two between 3 & 4. Thus, when partitioning onto this linear array of FPGAs, it is better to have two signals being communicated, one between 1 & 2, and one between 2 & 3, than it is to have a single signal communicated between 1 & 4. In order to do a reasonable job of partitioning onto a multi-FPGA system, the partitioner needs to be aware of the topology onto which it is partitioning. For this reason the step of global placement, the assigning of partitions to specific FPGAs in the system, is often done simultaneously with partitioning. Otherwise it is hard for a partitioner to understand the cost of communication within a given topology if it does not know where the partitions it is creating lie within this topology.

One method for performing partitioning onto a multi-FPGA systems is to handle it as a placement problem. Specifically, we can apply simulated annealing to the partitioning problem, allowing the tool to assign logic to specific FPGAs in a multi-FPGA system [Roy94, Roy-Neogi95]. Just as in placement for single FPGAs, the tool randomly assigns logic to functional units, which in this case are the logic-bearing FPGAs. The logic assigned to an FPGA is restricted to the FPGA's capacity. The partitioner then uses the simulated annealing algorithm to seek better placements through random moves under an annealing schedule. However, one problem with partitioning onto a multi-FPGA topology is that it can be difficult to estimate the routing costs of a given assignment. In an FPGA, routing distances tend to obey a simple geometric cost metric, with the physical distance between source and sink directly relating to the routing costs. In a multi-FPGA system, there may be an arbitrary connection pattern between FPGAs, with no simple geometric cost metric accurately capturing the actual routing complexity. However, in meshes and other regular architectures, geometric routing cost metrics can be developed, and simulated annealing or other algorithms can be applied. Another possibility for such a system is the partitioner for the Anyboard system [Thomae91, Van den Bout92, Van den Bout93], which applies a variant of the Kernighan-

Lin algorithm [Kernighan70] to a bus-structured multi-FPGA system where interconnect costs are easily determined.

In order to handle the partitioning problem on topologies that do not admit a simple routing cost metric, it is necessary to come up with some other method of estimating routing complexity. One method is to model the routing problem as a multicommodity flow problem and use this as part of the partitioning process [Vijayan90]. The multicommodity flow problem can estimate the routing complexity on a general graph, meaning that this approach can be used on an arbitrary multi-FPGA topology. However, the flow calculation can be very complex, and thus cannot be used in the inner loop of a complex partitioning algorithm. Thus, the flow calculation is only run after a significant number of iterations of a normal algorithm, which uses the previous flow calculation as an estimate of current routing conditions. However, even with this modification, their algorithm has an exponential worst-case complexity.

Although the approaches discussed previously can develop reasonably accurate estimates of partitioning quality, they take a significant amount of runtime to complete. The approach in [Vijayan90] has an exponential worst-case complexity, and simulated annealing is notoriously slow. An alternative to both of these algorithms is to adapt the standard partitioning algorithms [Alpert95], which ignore interconnection limitations, to partitioning onto a topology. For crossbar topologies, multi-way partitioning algorithms can be directly applied. In a crossbar topology [Hauck98] routing costs are adequately captured by the amount of inter-FPGA signals connected to each logic-bearing FPGA in the system, which is the optimization metric of many multi-way partitioning algorithms. For a hierarchical crossbar (which has multiple standard crossbar topologies connected together by higher levels of crossbar interconnections) multi-way partitioning algorithms can be recursively applied. In a hierarchical crossbar there are N subsets of the topology interconnected in the highest level in the crossbar. Minimizing the communication between these N subsets is the primary concern in a hierarchical crossbar, because the connections at the highest level of a hierarchical crossbar tend to be the primary routing bottleneck. Thus, a multi-way partitioning algorithm can split the circuit into N pieces, one per subset of the topology, and optimize for this bottleneck. At this point each of these subsets can be handled independently, either as a crossbar or a smaller hierarchical crossbar. In this way, standard multi-way partitioning algorithms can be recursively applied to a hierarchical crossbar, yielding a fairly fast partitioning algorithm.

**Figure 7.** An example of the suboptimality of recursive bipartitioning. We are partitioning to the multi-FPGA system at middle, and the best first cut is shown at left (gray line). The next partitioning would have to cut nine signals. We can instead partition as shown at right, cutting a total of two signals.

A similar recursive partitioning approach can be applied to other multi-FPGA system topologies. A split in the multi-FPGA topology is chosen that breaks the system into two or more subsets, and the logic is split into a similar number of pieces. These subsets are then subdivided repeatedly until the mapping has been broken into N pieces, one per FPGA in the system. By using a fast bipartitioning or multi-way partitioning algorithm, a complete

partitioning of the circuit onto the multi-FPGA topology can be performed. Such an approach has been used to quickly partition circuits onto the Teramac system [Snider95].

There are two problems with recursive bipartitioning onto a multi-FPGA system: it is greedy (overlooking more global concerns), and it ignores the multi-FPGA topology. It is greedy because the first bipartitioning attempts to find the best possible bipartitioning. While it may find a good way to split a mapping if it is only going to be broken into two parts, it may be a poor choice as a starting point for further cuts. The first split may require only a small amount of communication between the two halves of the system, but later cuts may require much more communication. We may have been better served having a somewhat larger initial cut, which might ease congestion on later cuts, and thus minimize the overall amount of inter-partition communication. An example of this is shown in Figure 7.

**Figure 8.** Example of iterative bipartitioning. The circuit (top left) is partitioned onto the multi-FPGA topology (bottom left) in a series of steps. Each partitioning corresponds to the most critical bottleneck remaining in the multi-FPGA system, and after each partitioning the placement of the logic is restricted to a subset of the topology (labeling on circuit partitions).

The greediness of iterative bipartitioning can be taken advantage of in order to map onto a specific multi-FPGA topology [Hauck95b]. Specifically, the multi-FPGA topology itself will have some bottleneck in its topology, some place where the expected communication is much greater than the routing resources in the multi-FPGA topology. For example, going back to the linear array of FPGAs discussed earlier (Figure 6), it is clear that if the number of wires connecting adjacent FPGAs is the same throughout the system, then the wires between the middle FPGAs, numbers 2 & 3, will be the most heavily used, since with an equal number of FPGAs on either side of this pair of FPGAs the communication demand should be the highest. Not all multi-FPGA systems will be linear arrays of FPGAs, but within most of them will be some set of links that are the critical bottleneck in the system. If we iteratively partition the circuit being mapped onto a topology such that the first cut in the circuit falls across this critical bottleneck, with the logic in one partition placed on one side of the bottleneck, and the other partition on the other side of the bottleneck, then this greedy early cut is performed exactly where the best cut is necessary. We can continue this process, performing partitionings corresponding to the remaining bottlenecks in the system. In this way we take advantage of the greedy nature of iterative bipartitioning, performing the early, greedy cuts where necessary to relieve the most significant bottlenecks in the topology, while later cuts (which are hurt by the greediness of earlier cuts) are performed where lower quality cuts can be tolerated, since they correspond to locations that are not critical bottlenecks in the system. An example of this process is shown in Figure 8. While this does not totally avoid the suboptimality of iterative bipartitioning, it does help limit it.

There are other ways of improving on the basic hierarchical greedy scheme. In [Kim96], Kim and Shin present algorithms in which a first cut hierarchical partitioning phase is followed by a second pass iterative optimization phase in which all constraints are satisfied. Chou et al. [Chou94] present a scheme that uses a local ratio-cut clustering followed by a set covering partitioning method. [Kuznar94] uses functional replication to improve the quality of partitioning.

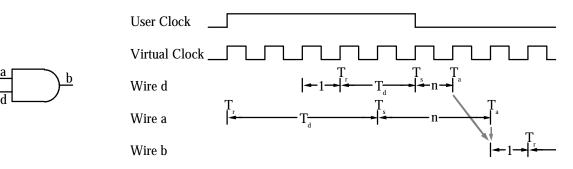

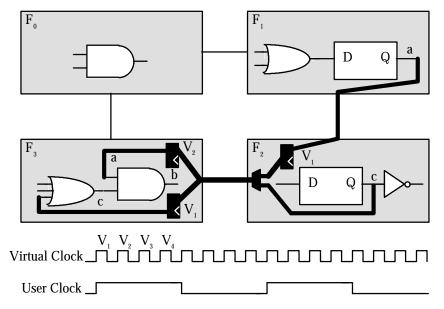

#### 4.2.1 Partitioning for VirtualWires

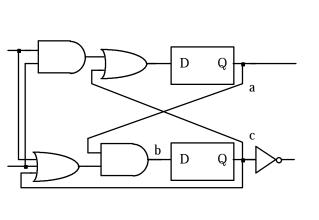

The gate versus IO requirements for partitioned blocks are often mismatched with the gate versus IO balance in commercial FPGAs. Generally, experience has shown that for a given number of gates, partitioned blocks tend to have more IOs than FPGAs do. A compilation technique called VirtualWires [Babb93] attempts to bridge this gap through a multiplexing and pipelining approach that enables superfluous gates on FPGAs to be traded for pins, thus allowing more efficient use of FPGA resources. The basic idea is that when the number of logical signals that must cross partitioned boundaries is greater than the number of physical pins on an FPGA, the VirtualWires technique multiplexes and pipelines several logical signals on each physical FPGA pin. Consequently, the multiplexors allow more logical signals to cross FPGA boundaries, but incur a gate cost that is proportional to the number of logical signals onto a single physical pin is orchestrated against a discrete time-base provided by a new clock called the virtual clock. A VirtualWires compiler schedules both logic evaluation and communication on specific cycles of the virtual clock. Scheduling is discussed further in Section 4.3.3.

Partitioning algorithms for VirtualWires are modified forms of those used in traditional systems, differing largely in the cost constraints or the optimization criteria they use during the optimization process [Agarwal95]. Let us represent partitioning constraints as follows. Suppose  $G_i$  is the number of gates in partition *i*, and  $P_i$  is the number of pins in partition *i*. Also suppose that  $G_{max}$  and  $P_{max}$  are the maximum number of gates and pins (respectively) that an FPGA can support.

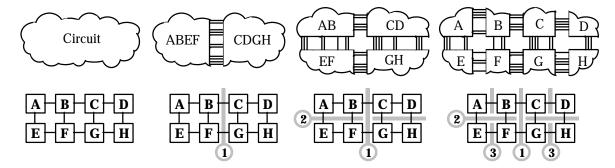

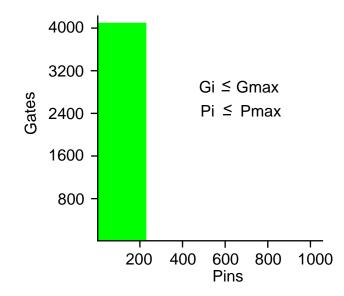

In a traditional system, the constraints faced by the partitioner are:  $G_i = G_{max}$  and  $P_i = P_{max}$ . The constraints are graphically represented in the left hand side of Figure 9 showing the feasible partitioning region in terms of gates and pins. Partitioning attempts to divide a set of gates into the minimum number of partitions that satisfy the above constraints. Typically, the traditional process involves dividing the number of gates into some number of partitions in a manner that satisfies the gate constraint, and then moving gates between partitions to minimize the number of pins in an attempt to satisfy pin constraints.

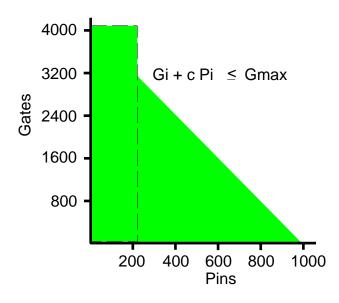

Now, let us consider the VirtualWires case. Let *c* denote the "cost" in terms of logic gates of a virtual wire. In other words, let *c* represent the average number of overhead logic gates in a VirtualWires system that are required to implement a single logic signal that must be sent or received by an FPGA (for simplicity, we assume that both inputs and outputs cost the same). In our experience *c* is roughly four gates. In a VirtualWires system, the constraint faced by the partitioner is  $G_i + c P_i$   $G_{max}$ . The resulting constraint space for the VirtualWires case is denoted in Figure 10. As can be seen, because pin constraints can be folded into a gate constraint, the feasible space is larger with VirtualWires. The intuition why the feasible space is larger is that gates can be traded for pins. If a given partition has more pins than the others, then the increased number of pins can be compensated for by placing fewer gates on that FPGA.

As before, partitioning attempts to divide a set of gates into the minimum number of partitions that satisfy the above constraint. VirtualWires partitioning involves dividing the number of gates into some number of partitions and then moving gates between partitions to reduce the number of IO so that the above gate constraint is satisfied for each partition. The partitioning algorithm itself can be one of those described earlier.

## 4.2.2 Global Placement

The placement of partitions on FPGAs can be accomplished as a separate, standalone phase in the compilation process, or it can be combined with partitioning. A separate placement phase simplifies the software system, but the overall results are generally poorer. The placement process assigns partitions to FPGAs. Placement attempts to put partitions that communicate intensely or partitions that are in timing critical paths as close together as possible. Because the placer must attempt to optimize several criteria, such as global communication volume and the critical path length, simulated annealing is a commonly used technique.

Figure 9. Constraints used by a traditional partitioner.

Figure 10. Constraints used by a VirtualWires partitioner.

To apply simulated annealing to the multi-FPGA placement problem requires both a cost function and a move function. The move function for a multi-FPGA system usually involves simply swapping the contents of two FPGAs. Developing a cost function for this problem is more difficult, since considerations such as critical path length and routing congestion must often be considered.

An important factor in such algorithms is that the move generator be able to estimate the move cost quickly - a move function that requires recalculating the routing of the entire system after each move is impractical. Unfortunately, to compute the true routing complexity or critical path length for a given configuration of the system requires just such an action - the swap of two partitions between FPGAs can significantly change most routing-related costs. Estimates can be made by ignoring congestion, and assuming all routes can take the minimum path between FPGAs. However, if there is routing congestion due to a given placement of the logic, this routing estimator will ignore this effect, and yield an overly optimistic cost metric. Thus, the simplicity of separating the partitioning and global routing steps must be balanced against the potential for lower-quality results due to inaccurate cost metrics.

#### 4.3 Global Routing

Global routing is the process of determining through which FPGAs or interconnection switches to route inter-FPGA signals. Note that the related problem of determining which specific pins to use to carry a signal is often handled separately; it will be discussed later in this paper. In cases where a signal needs to connect between only two directly connected FPGAs, this step is usually simple. No intermediate FPGA is needed to carry this signal, and the routing can be direct. However, in some cases the wires that directly connect these FPGAs may be used up by other signals. The signal will need to take alternate routes, routes that may lead through other FPGAs. For long-distance routing, there may be many choices of FPGAs to route through. A global router attempts to choose routes in order to make the most direct connections, thus minimizing delay and resource usage, while making sure that there are sufficient routing resources to handle all signals.

Routing is a problem in numerous domains, including standard cells, gate arrays, circuit board layout, and single FPGAs. Global routing for multi-FPGA systems is similar to routing for single FPGAs. Specifically, in an FPGA the connections are fixed and finite, so that the router cannot add resources to links that are saturated, and the connections may not obey strict geometrical distance metrics. The same is true for a multi-FPGA system. In the cases of standard cells and gate arrays, the size of routing channels can (usually) be increased, and in circuit board routing extra layers can be added. Thus, for multi-FPGA global routing many of the techniques from single-FPGA routing are also applicable.

In the sections that follow we will discuss routing algorithms for several different types of systems, including crossbar and direct-connect systems. We will also consider global routing for Virtual Wires systems.

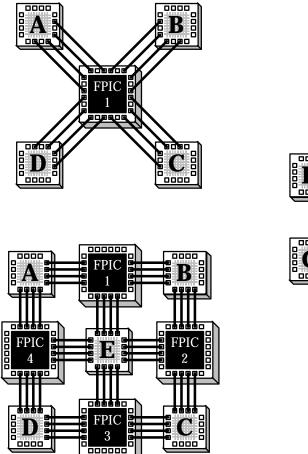

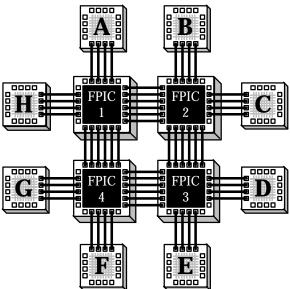

**Figure 11.** Crossbar routing topology. The chips at top are used purely for routing, while the FPGAs at bottom handle all the logic in the system.

#### 4.3.1 Global Routing for Crossbar Topologies

In a crossbar topology (Figure 11), a signal that needs to be routed between FPGAs will always start and end at logic-bearing FPGAs, since routing-only chips have no logic in them. Thus, routing any signal in the system, regardless of how many FPGAs it needs to connect to, requires routing-only chip exactly one other chip, and that chip can be any of the routing-only chips. This is because each routing-only chip connects to every logic-bearing FPGA, and the routing-only chips have exactly the same connectivity. Thus, routing for a crossbar topology consists simply of selecting which routing-only chip an inter-FPGA signal should route through, and a routing algorithm seeks only to route the most number of signals. Note that this does require some effort, since some assignments of signals to routing-only chips allow much less communication than others. For example, assume that each of the connections between chips in Figure 11 consist of 3 wires, and assume that we are attempting to route three-terminal wires, with connections evenly distributed between the logic-bearing FPGAs. If we route signals between FPGAs **ABC** through W, **ABD** through X, **ACD** through Y, and **BCD** through Z, we will be able to route three signals through each routing-only chip, for a total of 12 signals. At this point, no further routing can

be performed, even of two-terminal wires. We can instead route one **ABC**, one **ABD**, one **ACD**, and one **BCD** wire through each of the routing-only chips, achieving a total of 16 routed signals.

There have been several algorithms proposed for the routing of signals in crossbar topologies. [Mak95b] presents an algorithm that is optimal for 2-terminal routing, as well as proof that routing for multi-terminal nets is NP-Complete. The routing algorithm is based on the idea that if too many routes are assigned to a given routing-only chip, there must be some routing-only chip that is underutilized. Otherwise, there would be no possible routing for this mapping. Given this fact, the routes going through these two chips can be balanced, so that there is almost an identical number of nets going to each of these routing-only chip from each logic-bearing chip. Thus, to perform the routing for a crossbar topology, simply assign all of the nets to a single routing-only chip, and then iteratively balance the demand on routing-only chips until the routing is feasible. Since the problem of routing multi-terminal nets in a crossbar topology is NP-Complete, heuristic algorithms have been proposed [Butts91, Kadi94]. These greedily route signals through routing-only chips based on their current utilization. Because of this, they may not always find a routing solution in situations where such a solution exists, even in the case of purely 2-terminal routing. Thus, there may be some benefit in combining a heuristic approach to multi-terminal net routing with the optimal approach to 2-terminal net routing, though it is not clear how this could be done. An alternative is to break all multi-terminal nets into a spanning tree of only two-terminal nets. Then, the optimal algorithm can be applied to routing these 2-terminal nets. [Mak95a] proposes an algorithm which will perform such a decomposition, as well as make sure that the I/O capacity of the FPGAs are not violated by the splitting of multiterminal nets. However, this decomposition requires extra I/O resources on some FPGAs in the system to accomplish this splitting, and if such resources are not available, this algorithm cannot find a routing, even though such a routing may in fact exist for non-decomposed multi-terminal nets.

#### **4.3.2** Global Routing in Direct-Interconnect Systems

Thus far we have looked at routing for indirect interconnects. Indirect interconnection systems are those in which logic bearing FPGAs are distinct from FPGAs or switches that handle routing tasks. Routing with direct interconnects is a little more complicated. In a direct interconnect hardwire system, routing is the problem of selecting the set of FPGAs through which to route a signal between a pair of partitions. The following algorithm describes a routing approach for direct interconnect hardwire systems. We first present a simple approach and then suggest methods to improve the route quality.

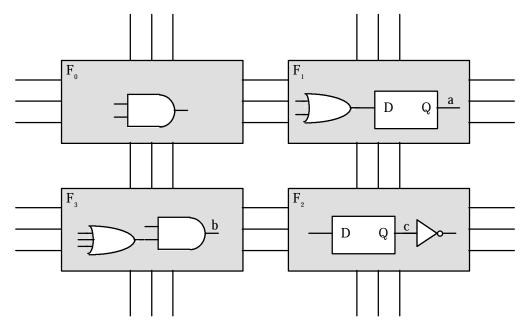

This routing method begins by constructing the *FPGA channel graph*. This is a directed graph that represents the FPGA topology in which each node represents an FPGA and each directed edge represents a channel. A channel is the set of directed connections from one FPGA to another. Each channel has a width representing the number of physical wires in the channel. The use of directed channels with predetermined widths is a simplification because the IO pins in typical FPGAs can be configured to behave as either outputs or inputs. Figure 12 shows an example input circuit that we wish to map onto a mesh connected FPGA topology. The channel graph for the FPGA topology is shown in Figure 13. The latter figure also shows the initial values of the available channel capacities.

Figure 12. Input circuit (left) and FPGA topology (right).

Figure 13. FPGA channel graph showing the initial values of the available channel capacities.

The algorithm also relies on a *distance weight* and the *available channel capacity* of each channel in the channel graph. For channel *C*, let  $C^d$  represent the distance weight, let  $C^w$  represent the physical channel width, and let  $C^a$  represent the available channel capacity. Distance weights are used to turn off channels that are full. Assign a default distance weight of 1 to each channel and initialize the available channel capacity to the channel width. In other words, initialize,

$$C^{d} = 1$$

$$C^{a} = C^{w}$$

The algorithm works by repeated applications of the following step: pick a wire and find a route comprising a sequence of channels from its source partition to its destination partition. If a net has d > 1 destination terminals, then the router can treat the net as d two-terminal wires, each of which connects the source terminal to one of the destination terminals.

More specifically, the algorithm applies the following step until all nets have been assigned a route.

- 1. Pick a wire and find the partition that sources the net. Let *s* denote the source partition and let  $s_f$  denote the FPGA on which the source partition is placed. Similarly, let *d* be the destination partition for the net and let  $d_f$  be the FPGA on which the destination partition lies.

- 2. Find the shortest path  $P_{sd}$  (using a standard shortest path algorithm, where  $\frac{d}{i}$

4. Associate the path  $P_{sd}$  with the wire and mark the wire so it is not picked again.

As an example, suppose the design in Figure 12 is partitioned and placed as in Figure 14. Also suppose that the wire *a* is the first wire picked to be routed. The source FPGA  $s_f$  for this wire is F1 and the destination FPGA  $d_f$  is F3. The initial state of the channel graph is as shown in Figure 13. The state of the graph after wire *a* is routed is shown in Figure 15. Figure 16 shows a possible routing of all the nets.

Figure 14. A partition and placement of the input circuit.

Figure 15. Channel graph showing available channel capacities after routing the net a.

The above algorithm can be optimized in many ways. For example, consider this optimization for multi-terminal wires *n* that are represented as *d* two-terminal wires  $n_1$ ,  $n_2$ ,  $n_3$ , ...  $n_d$ . Suppose that the two-terminal wires  $n_1$ ,  $n_2$ , ...  $n_{i-1}$  have been previously routed, and we are attempting to route wire  $n_i$ . We can choose as the source FPGA for  $n_i$  any of the FPGAs that are connected by wires  $n_1$ ,  $n_2$ , ...  $n_{i-1}$ , potentially saving valuable channel capacity.

In a direct-interconnect system, the channels can sometimes run out of capacity and the global router can fail to find any path to route a given wire. The router can attempt to make further progress by ripping out one or more previously assigned routes to make space in the congested channel and unmarking the related wires. However, because pin usage for routing hops in a direct interconnect system is related to the characteristics of the input

netlist, providing guarantees of routing success is impossible. Repartitioning the netlist for a larger number of FPGAs can exacerbate the problem because of the increased routing distances and the associated increase in hop-related pin requirements. Consequently, large multi-FPGA systems often resort to indirect interconnection networks.

Figure 16. A routing of the input circuit on the target topology.

The global router in hardwire systems must also attempt to satisfy hold time constraints in gated clock designs. For correct operation, the edge-triggered flip-flop discipline requires that the input signal be valid for a period of time — called the *hold time* — following the occurrence of the edge on the flip-flop clock terminal. In a typical VLSI design, the user or the layout tool is responsible for laying out the signal wires and controlling delays so that hold times are met. FPGAs provide special controlled delay clock signal lines for routing clocks to flip-flops in FPGAs so they meet hold times when the design is mapped onto FPGAs. However, when flip-flops are clocked by a gated clock signal derived as some combinational function of a clock and user design signals and is routed over normal FPGA routing logic there is the danger that the hold times will not be met. This situation is exacerbated when the design spans multiple FPGAs, where it is even harder to control delays. In such situations, the global placer and router must arrange the lengths of the signal and gated clock paths (perhaps padding the input signal path with extra delay) so that hold times are satisfied.

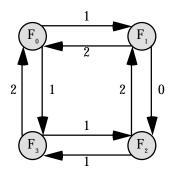

#### 4.3.3 Global Routing and Scheduling in VirtualWires systems

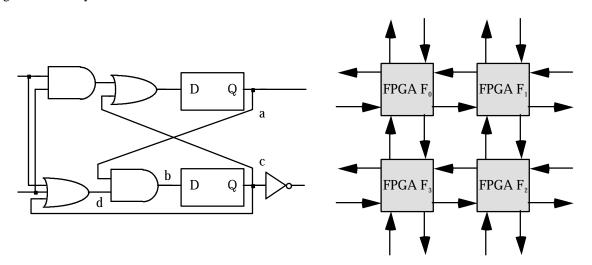

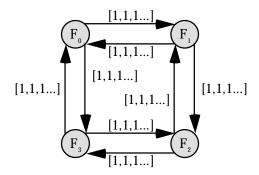

Global routing for VirtualWires systems is also called global scheduling because it includes a time dimension and produces a source-destination path in time and space. The scheduler in VirtualWires systems is also responsible for the correct ordering of logic evaluation and communication events, and relies on a digital abstraction of time and space for both simplicity and reliability.

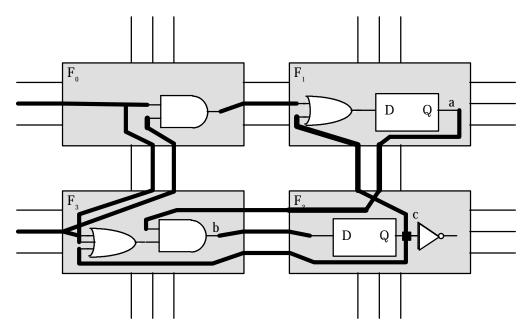

**Time and Space Digitization** Recall that VirtualWires systems multiplex the physical wires in the inter-FPGA channels so that the number of signals that can be communicated within a single cycle of the user's clock is not bounded by the channel capacities. Sharing of physical wires and scheduling of computation and communication is governed by a virtual clock that provides a discrete time-base. Computations and possible registration of signals within an FPGA take place during a specific sequence of virtual clock cycles prescribed by the scheduler. Thus each cycle of a user's clock is digitized into multiple virtual clock cycles.

In addition to time discretization, VirtualWires systems digitize space as well. Each signal is registered at FPGA boundaries in a flip-flop synchronous to the virtual clock, and is communicated between a pair of FPGAs over a

physical wire on a given virtual clock cycle. Thus, all combinational timing paths are entirely within individual FPGAs. Timing paths also involve inter-FPGA crossings between directly connected FPGA pairs. Such a digital space abstraction not only provides a simple model to the scheduler, but yields system composability in which local timing correctness guarantees global timing correctness.

**Timing Resynthesis** To facilitate complete event ordering control, all clocked elements in the system are resynthesized to use the virtual clock or signals synchronous to the virtual clock. As part of its routing process, the scheduler establishes the specific virtual cycle on which each storage element is enabled.

**The TIERS Routing Approach** The goal of the scheduler is to orchestrate all events in the system. In other words, it must prescribe the specific set of virtual clock cycles and the physical channels on which inter-FPGA signals are communicated. Because a physical channel wire is allocated to a given signal only during a specified virtual clock cycle, and not dedicated for all time, the scheduler must also determine the virtual cycle on which the given signal reaches its legal value and can be sampled for transmission outside the chip. The following is a simplified version of the TIERS algorithm for scheduling VirtualWires systems. For more details on TIERS (Topology Independent Pipelined Routing and Scheduling) see [Selvidge95].

The TIERS routing approach comprises the following steps:

- 1. Construct the FPGA channel graph.

- 2. Order inter-partition wires through a dependence analysis.

- 3. Determine the time-space path for each wire.

As with direct-interconnect systems, we first construct the FPGA channel graph. Each channel comprises a given number of wires. Although each wire is assumed to be able to carry a single signal during a given virtual clock cycle, each wire has an unbounded temporal extent. In other words, a given wire can transmit more signals by using additional virtual cycles. Because channels can yield more capacity by using more virtual clock cycles, the simplest VirtualWires scheduling algorithm does not require distance weights on the channels. Recall the distance weights are used by hardwire routers to disconnect full channels.

Figure 17. Input circuit (left) and FPGA topology (right).

The available channel capacity in VirtualWires systems is a function of the virtual clock cycle. In other words, each channel has a specific available channel capacity for a given virtual clock cycle. We use a dynamic array indexed by the virtual clock cycle for the available channel capacity, and initialize each element to the channel width. In other words, let  $C^{w}$  represent the physical channel width of channel C, and let  $C^{a}(t)$  represent the available channel capacity, for all channels, initialize

$$C^{a}(t) = C^{W} \quad \forall t$$

Consider the same input circuit as before, but a FPGA topology with fewer physical connections as in Figure 17. The channel graph for this topology for use in VirtualWires routing is shown in Figure 18.

**Figure 18** FPGA channel graph showing the initial values of the available channel capacities as a function of the virtual cycle. Initially,  $C^{a}(t)$  for each channel is 1 for all values of t.

Figure 19. The relationship between the various scheduling times for signals a, d, and b. Wire b depends combinationally upon a and d, and a is produced as the output of a flip flop.

The second step involves ordering inter-partition wires through a dependence analysis. In a discrete event system, the scheduler must guarantee that signals that are inputs to a combinational logic block must be available before the outputs of the combinational logic block can be routed. It does so by routing all input wires *before* routing any of the output wires of any combinational block. System input wires and flip-flop output wires comprise the initial conditions for the recursive process implied by the above precedence constraint. A routing order consistent with the above constraint is facilitated by creating a sorted list of inter-partition wires in which a wire  $w_i$  precedes another wire  $w_j$  only if  $w_i$  does not depend combinationally on  $w_j$ . We also associate with each output wire of a partition the set of partition input wires on which it depends. As an example, wire *a* (shown in Figure 17) must be scheduled before wire *b* because *b* depends combinationally upon *a*.

The third step involves finding time-space routes for inter-partition wires. The routing algorithm does so by performing the following sequence of operations to wires picked in order from the sorted list of wires, until all wires have been assigned a time-space route. A time-space route comprises a sequence of channel and virtual-cycle pairs from the source FPGA to the destination FPGA. As before, the router treats a net with d > 1 destination terminals as d two-terminal wires, each of which connects the source terminal to one of the destination terminals.

- 1. Find the partition that sources the wire. Let *s* denote the source partition and let  $s_f$  denote the FPGA on which the source partition is placed. Similarly, let *d* be the destination partition for the wire and let  $d_f$  be the FPGA on which the destination partition lies.

- 2. Find the shortest path  $P_{sd}$  (using a standard shortest path algorithm) between FPGAs  $s_f$  and  $d_f$ .  $P_{sd}$  is simply the sequence of channels  $C_i$ :  $i = 0 \dots n-1$  in the shortest path between FPGAs  $s_f$  and  $d_f$ .

The next set of steps determines the scheduling of the signals along the sequence of channels, and establishes the ready time, arrival time, and send time for the signal (see Figure 19).

3. Determine the *ready time*  $T_r$  for the wire. The ready time of a wire is the earliest virtual cycle on which the wire attains its legal value. The ready times on system input wires and wires sourced by flip-flops is initialized to 1. The ready times for other wires is one plus the maximum of the *arrival times* of the wires on which they depend. The one extra cycle allows for local combinational computation and registration of the signal in a flip-flop just prior to transmission through an FPGA output pin.

The *arrival time*  $T_a$  of a wire at an FPGA is the time (or virtual cycle) at which the signal on the wire will arrive at that FPGA. Assuming there are no combinational cycles in the circuit, picking wires according to the order in the sorted wire list guarantees their ready time can be calculated.

4. Compute the *departure delay*  $T_d$  for the wire. The departure delay is the number of cycles the wire is delayed at the FPGA as it waits for the availability of a sequence of available time slots along the path  $P_{sd}$ .

One variant of the routing algorithm [Selvidge95] adds delays to a wire only at the source FPGA. That is, once a signal is scheduled for routing it suffers no additional delays till it reaches its destination FPGA. With the source-delay algorithm, a workable route can be obtained by looking for available channel capacity in each of the channels in  $P_{sd}$  during successive time slots starting with the ready time  $T_r$  of the wire (i.e., for  $T_d = 0$ ). If the signal is not routable starting at  $T_r$ , then the departure delay is increased until a workable route is found.

More formally, a wire is routable with departure delay  $T_d$  if the following is true:

$$C_i^a(T_r + T_d + i) \ge 0, \ i = 0 \dots n - 1$$

The above assumes the each hop is accomplished in one virtual cycle.

5. Compute the *send time*  $T_s$  for the wire. The send time for a wire is the sum of the ready time and the departure delay for the net.

$$T_s = T_r + T_d$$

6. Compute the *arrival time* of the net at the destination FPGA. Because our routing model assumes that delays are added only at the source, the arrival time is simply the sum of the send time and the number of hops *n*. In other words, if the number of channels in  $P_{sd}$  is *n*,

$$T_a = T_s + n$$

7. Decrement the available channel capacity for each channel in  $P_{sd}$  for the time slot on which it is used by the net.

$$C_i^a(T_s + i) = C_i^a(T_s + i) - 1, \ i = 0...n - 1$$

When the available channel capacity of any channel *i* during a time slot *t* is exhausted, i.e.,  $C_i^a(t) = 0 C^a(t) = 0$ , that channel will not be selected for further routing during time slot *t*.

8. Associate the path  $P_{sd}$ , the send time  $T_s$ , and the arrival time  $T_a$  with the net. The  $T_s$  time is needed by a future VirtualWires synthesis step that actually implements FPGA-specific state machines and enables appropriate flip-flops and multiplexing logic on the appropriate virtual cycle.  $T_a$ , on the other hand, is needed to compute the ready time of other nets that depend on it.

As an example, consider wires *a*, *b*, and *c* shown in Figure 17. One possible ordering of the wires in the depend sorted wire list is *a*, *c*, *b*.  $T_r$  for both *a* and *c* is 1 because both are sourced by a flip flop in the original design. Since both can be scheduled for transmission immediately  $T_d$  for both is 0, and therefore  $T_s$  for both is 1 As depicted in Figure 21, the wire *a* can be scheduled on the channel from F1 to F2 on virtual cycle 1 and on the

channel from F2 to F3 on the following virtual cycle. Thus,  $T_a$  for *a* is 3 since *n* (the number of hops) is 2. The channel graph following the scheduling of *a* is as shown in Figure 20. Similarly, wire *c* can be scheduled on the channel from F2 to F3 on virtual cycle 1.  $T_r$  for wire *b* can be calculated as 3 (one plus the arrival time for *a*). Because the channel from F3 to F2 is available,  $T_d$  for *b* is 0, and *b* can be scheduled on virtual cycle 3.

**Figure 20.** FPGA channel graph showing the values of the available channel capacities after wire *a* has been scheduled.

As part of its routing process, the scheduler also establishes the specific virtual cycles on which the resynthesized storage elements must sample their inputs. It particular, it uses the arrival times of signals at an FPGA to compute the ready times of signals at inputs of storage elements, and thereby obtains a lower bound on the time those storage can sample their inputs. Similarly, it also ensures that flip flops hold their values at least until the send time  $T_s$  of the corresponding signal. Because the scheduler exercises complete control on when flip flops are enabled for gated-clock designs, and when signals arrive as inputs to flip-flops, hold time problems are also eliminated [Selvidge95]. See [Agarwal95] for a more detailed discussion on this material.

**Figure 21.** Virtual routing of wires a and c. On virtual cycle V1, the signal on wire a is routed from F1 to intermediate hop F2, and the signal on wire c is routed from F2 to F3. The figure also shows the multiplexing and hop logic introduced by VirtualWires to implement the routing and scheduling.

Improvements to the basic routing technique discussed above are described in [Selvidge95]. One improvement, called critical path sensitive routing, attempts to route critical path nets before other nets. Recall that the wires are scheduled in dependence partial order. When several candidate wires are routable according to the partial order, critical path sensitive routing selects the wire with the greatest depth, that is, one that belongs to a combinational path with the largest number of FPGA crossings. Experience has shown that critical path sensitive TIERS

typically produces schedules that come close to the lower bound established by the length of the longest critical path in the design.

### 4.4 Pin Assignment

Pin assignment is the process of deciding which I/O pins to use for each inter-FPGA signal. Since pin assignment occurs after global routing, the FPGAs through which long-distance routes will pass have already been determined. Thus, if we include simple buffering logic in these intermediate FPGAs (this buffering logic can simply be input and output pads connected by an internal signal), all inter-FPGA signals now move only between adjacent FPGAs. Thus, pin assignment does not do any long-distance routing, and has no concerns of congestion-avoidance or resource consumption.

The problem of pin assignment has been studied in many other domains, including routing channels in ASICs [Cai91], general routing in cell-based designs [Yao88, Cong91], and custom printed circuit boards (PCBs) [Pförtner92]. Unfortunately, these approaches are unsuitable to the multi-FPGA pin assignment problem. First, these algorithms seek to minimize the length of connections between cells or chips, while in a multi-FPGA system the connections between chips are fixed. The standard approaches also assume that pin assignment has no effect on the quality of the logic element implementations, while in the multi-FPGA problem the primary impact of a pin assignment is on the quality of the mapping to the logic elements (individual FPGAs in this case). Because of these differences, there is no obvious way to adapt existing pin assignment approaches for other technologies to the multi-FPGA system problem.

Figure 22. Multi-FPGA topologies with simple pin assignments.