# Analysis and Design of a Transformer-Feedback-Based Wideband Receiver

Venumadhav Bhagavatula, Student Member, IEEE, and Jacques C. Rudell, Senior Member, IEEE

Abstract—This paper proposes a multistage transformer-feed-back-based design approach for a high fractional-bandwidth (fBW) IF stage in a 60-GHz heterodyne receiver. An in-depth analysis of source-to-gate transformer-feedback amplifiers, including the design of the matching network, is presented. Analytic expressions for the input resistance, quality factor, and noise figure (NF) as a function of the transformer turns-ratio (n) and magnetic coupling factor (k) are derived. To validate the proposed analysis, a wideband IF amplifier and mixer were designed in a 40-nm CMOS process. From measured results, this device achieves a 16% - 3-dB fBW, a peak power gain of 27.6 dB, an NF of 5.3 dB while consuming 28.8 mW from a 0.9-V supply.

Index Terms—CMOS, IF, Lange coupler, mixer, 60-GHz transceiver, source-to-gate transformer feedback.

#### I. INTRODUCTION

THE LAST decade has seen intense research efforts that seek to exploit both the high device  $f_t$  associated with modern CMOS technologies and the large bandwidth available at millimeter-wave frequencies to realize high data rate transceivers [1]–[4]. Specifically, the 7 GHz of unlicensed bandwidth from 57 to 64 GHz has attracted attention as a potential solution for short-range high-speed data communication links [2], [3]. Development of circuit techniques capable of handling modulated data with fractional bandwidths (fBWs), defined as (absolute bandwidth/center frequency), on the order of 15%–20% is crucial for these high data rate communication standards. The targeted data rates of up to 7 Gb/s have the potential to enable applications such as streaming uncompressed high-definition video [3] from a set-top box to a television, and communication between a portable smart-phone and a "Wireless Kiosk."

Imaging systems for medical and security applications have also benefited from wide bandwidth silicon integrated circuits (ICs). An active-imaging transmitter with pulse-widths as low as 26 ps, enabling free-space depth resolution of less than 4 mm, has been proposed in [4] for early breast-cancer detection. This transmitter requires circuits with a bandwidth and center frequency in excess of 30 and 75 GHz, respectively. In addition to

Manuscript received October 09, 2012; revised January 12, 2013; accepted January 15, 2013. Date of publication February 19, 2013; date of current version March 07, 2013. This work is an expanded paper from the IEEE RFIC Symposium, Montreal, QC, Canada, June 17–19, 2012.

The authors are with the Electrical Engineering Department, University of Washington, Seattle, WA 98195 USA (e-mail: bvenu@uw.edu; jcrudell@uw.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TMTT.2013.2244904

active imaging, a wideband passive-imaging receiver that collects millimeter-wave radiation emitted by objects to render an image has been reported [5] in the W-band (70–110 GHz).

In both of the above applications, the rate of data transfer and image resolution are enhanced by improving the bandwidth of the transceiver circuitry. At baseband frequencies, feedback techniques may be applied to extend the bandwidth of a circuit placed in a closed-loop configuration. However, in the past, limited power gain and  $f_t$  associated with CMOS transistors precluded the use of feedback techniques at RF frequencies. As a result, to realize a high fBW channel in CMOS, open-loop circuit techniques employing high-order LC-based ladder filters have been applied [6], [7]. Now, with advances in CMOS processing technology through silicon scaling, the device  $f_{\rm MAX}$  (unity power gain frequency) exceeds several hundred gigahertz, allowing designers to explore both resistive and reactive-feedback circuit techniques.

Reactive feedback using integrated transformers, in which the magnetically coupled windings provide a path for current-sense current feedback, has received considerable interest [8]–[10]. There are three fundamental transformer-feedback topologies [11]: drain-to-source, drain-to-gate, and source-to-gate. The first two, drain-to-source and drain-to-gate, have been applied in single-ended amplifiers to neutralize the  $C_{\rm GD}$  device capacitance and improve reverse-isolation over a wide bandwidth. The source-to-gate transformer-feedback (SGTxFB) topology is more suited for wideband matching network design and has been applied over a wide range of operating frequencies, ranging from ultra-wideband (UWB) [8] to W-band [9].

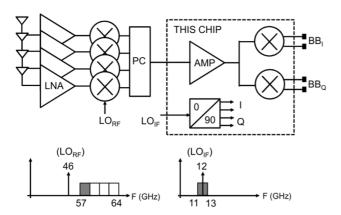

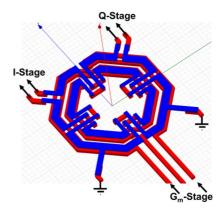

However, currently available analytic models for SGTxFB-based matching-network design provide little intuition for optimization. This paper provides a generic and systematic approach to the design of SGTxFB amplifiers. The input admittance is modeled as a function of transformer and transistor parameters. The models are then used to assess the impact of the circuit parameters on the bandwidth, noise figure (NF), and gain. In addition, application of SGTxFB in prior art has been restricted to the interface between the antenna and low-noise amplifier in integrated receivers. In contrast, this paper presents a multistage SGTxFB-based high-fBW IF stage for the 60-GHz heterodyne receiver shown in Fig. 1. Transformer feedback is employed to provide a wide bandwidth load on each circuit block in the receiver. The challenges involved in designing a multistage SGTxFB down-converter are described.

This paper is organized as follows. First, an ideal current-feedback amplifier (CFA) model is introduced, and related to a simplified first-order SGTxFB stage in Section II. Next,

Fig. 1. Heterodyne phase-array receiver: low-noise amplifier (LNA), power-combiner (PC) followed by a 11–13-GHz IF stage comprised of an IF amplifier, quadrature down-conversion mixer, and lumped-element Lange coupler for I/Q generation.

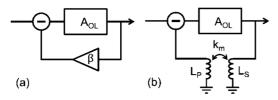

Fig. 2. (a) Generic feedback circuits. (b) Transformer-based feedback circuit.

guidelines for matching network design and accurate input admittance models for SGTxFB amplifiers are discussed in Section III. This is followed with a derivation of analytic expressions for the noise and gain of SGTxFB amplifiers in Section IV. The design of an IF stage, operating over a frequency range of 11–13 GHz, is described in Section V. Measured results from a prototype chip implemented in a 40-nm CMOS process are presented in Section VI. Finally, in Section VII, this paper concludes with some summary comments.

## II. CURRENT FEEDBACK

The generic model of a feedback system is shown in Fig. 2(a). The forward path consists of a high-gain amplifier,  $A_{OL}$ . A fraction of the output voltage (or current) of  $A_{OL}$  is sampled by the feedback circuit  $\beta$  and fed back to the input. In the circuit shown in Fig. 2(b), the feedback circuit  $\beta$  is a transformer; hence, the name transformer feedback. The secondary windings of the transformer samples the output current of  $A_{OL}$  and the current induced in the primary is fed back to the input. In the specific case of SGTxFB, the output current is sampled at the source and induced current is fed back to the gate of the MOSFET.

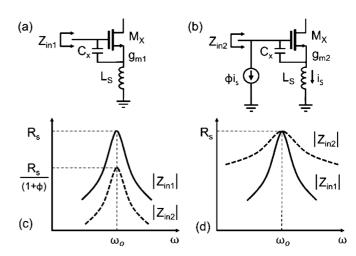

As a first-order approximation, an SGTxFB amplifier can be modeled as the CFA shown in Fig. 3(b). In this ideal current-feedback model, the feedback current induced in the primary  $(L_p)$  is included; however, the feed-forward current induced in secondary  $(L_s)$  is ignored. To study the impact of current feedback on bandwidth, consider the inductor-degenerated common-source amplifier (CSA) without and with current feedback shown in Fig. 3(a) and (b), respectively. Starting with

Fig. 3. (a) Common-source (CS) amplifier with inductor degeneration. (b) CS amplifier with inductor degeneration and current feedback. (c) Input impedance  $(Z_{\rm in})$  with  $g_{m1}=g_{m2}$ . (d)  $Z_{\rm in}$  with  $g_{m2}=g_{m1}(1+\phi)$ .

the circuit in Fig. 3(a), it is straightforward to prove that the input impedance  $Z_{\rm in1}$  is described by

$$Z_{\rm in1} = \frac{L_s g_{m1}}{C_X} + j\omega_o L_s + \frac{1}{j\omega_o C_X}.$$

(1)

Accordingly, the circuit appears to be a series-RLC network with  $\text{Re}\{Z_{\text{in}1}\}=(g_{m1}L_s)/C_X$ , resonant frequency  $\omega_o=1/\sqrt{L_sC_X}$ , and a quality factor  $Q_1$ , where

$$Q_1 = \frac{\omega_o L_s}{\text{Re}(Z_{\text{in}1})} = \frac{1}{g_{m1}} \sqrt{\frac{C_X}{L_s}}.$$

(2)

Next, consider the CFA in Fig. 3(b), where  $\phi$  describes the ratio of the source current  $i_s$  to the current fed back to the gate. The CFA and inductor-degenerated amplifier have identical  $L_S$ ,  $C_X$ , and  $M_X$ ; however, the devices are biased differently, and hence, have differing transconductance. The input impedance  $Z_{\rm in2}$  is given by

$$Z_{\text{in2}} = \frac{1}{sC_X} + \frac{\frac{g_{m2}}{sC_X} + 1}{1 + \phi \left(\frac{g_{m2}}{sC_X} + 1\right)} sL_S - \frac{\frac{g_{m2}}{sC_X} + 1}{1 + \phi \left(\frac{g_{m2}}{sC_X} + 1\right)} \frac{\phi}{sC_X}.$$

(3)

At  $s=j\omega_o,\ g_{m2}/(sC_X)=1/Q$ . Accordingly, for circuits with quality factor Q>4, the complex term in the denominator  $|1-jg_{m2}/\omega_o C_X|$  is approximately equal to 1; reducing (3) to

$$Z_{\rm in2} = \frac{1}{j\omega_o C_X} \frac{1}{(1+\phi)} + \frac{g_{m2}L_s}{C_X(1+\phi)} + \frac{j\omega_C L_s}{1+\phi}.$$

(4)

Thus, similar to (1), the input impedance of the CFA appears as a series RLC circuit resonant at  $\omega_o$ . In addition, it can be observed that the CFA has a input impedance  $\mathrm{Re}\{Z_{\mathrm{in}2}\}=g_{m2}L_s/(C_X(1+\phi))$  and quality factor  $Q_2$ , where

$$Q_2 = \frac{1}{g_{m2}} \sqrt{\frac{C_X}{L_s}}. (5)$$

Several important observations can be made based on the above result. Assume the circuit in Fig. 3(a) is designed to match with an antenna with resistance  $R_S$ , i.e.,  $R_S = \mathrm{Re}(Z_{\mathrm{in}1})$ . The first case to consider is wherein the transconductance of  $M_X$  is identical in both circuits  $(g_{m1} = g_{m2})$ . The resulting input impedance as a function of frequency is plotted in Fig. 3(c). From (2) and (5), one can observe that, with equal transconductance, both the amplifiers display an identical quality factor  $(Q_1 = Q_2)$ . However,  $\mathrm{Re}(Z_{\mathrm{in}2}) = R_S/(1+\phi)$ , as a result the CFA is not power matched to the antenna.

To correct the antenna mismatch, without altering the value of passive components  $L_s$  and  $C_X$ , transistor  $M_X$  in the CFA is biased such that  $g_{m2}=g_{m1}(1+\phi)$ . From (4), one observes that the new bias condition ensures  $\mathrm{Re}(Z_{\mathrm{in2}})=\mathrm{Re}(Z_{\mathrm{in1}})$ . Furthermore, since the quality factor of the matching network is inversely proportional to the transconductance, the  $g_m$ -boost results in a  $(1+\phi)$  reduction in the quality factor. Therefore, as compared to the inductor-degenerated CSA, the CFA effectively achieves a  $(1+\phi)$  higher matching bandwidth at the expense of  $(1+\phi)^2$  higher current (assuming square-law devices). This relative performance is shown in Fig. 3(d).

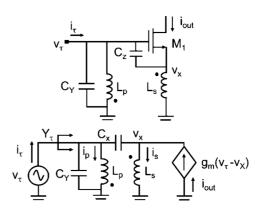

The desire to exploit current feedback to achieve a wide input matching bandwidth motivates application of SGTxFB. The SGTxFB amplifier in Fig. 4 contains two feedback loops. In the first feedback loop, at frequency  $\omega_o$ ,  $L_s$ senses the (output) current flowing through  $M_1$  and converts it to a voltage, which controls the (input)  $V_{\rm GS}$  of the device. In the second loop, current through  $L_s$  is fed back to the input via the antiphase mutual magnetic coupling between  $L_p$  and  $L_s$ . In effect, the transformer formed by  $L_s$  and  $L_p$  provides current-sense current feedback.

To design a matching network using SGTxFB, an accurate model of the input impedance of the amplifier as a function of transformer and transistor parameters is derived in Section III.

## III. SGTxFB-BASED MATCHING NETWORKS

Although receiver front-end circuitry realized with SGTxFB amplifiers has been reported in recent literature [8]–[10], insightful and compact analytic expressions that assist matching network design and model the noise performance are yet to be presented. This is primarily due to relatively open design space, comprising multiple variables such as device transconductance  $(g_m)$ , self-inductance  $(L_p, L_s)$ , and mutual inductance (M). To simplify the calculations, it is common to assume perfect magnetic coupling; a coupling coefficient  $(k=M/\sqrt{L_pL_s})$  of one. However, for a large turns ratio  $(n=\sqrt{L_p/L_s})$ , a coupling coefficient close to unity is difficult to achieve. To investigate the tradeoffs involved in the design of an SGTxFB, an input admittance model  $Y_\tau = f\{\omega_o, n, k, g_m, L_s\}$  is computed next.

#### A. Input Admittance

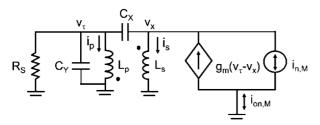

The small-signal model of the SGTxFB amplifier is presented in Fig. 4. Transistor  $M_1$  is assumed to have zero output conductance. In the small-signal model,  $C_X$  is the parallel combination of the gate-to-source capacitance  $(C_{\rm GS})$  of  $M_1$  and an extra capacitance  $C_Z$ . For the input admittance analysis, capacitance  $C_Y$ , which appears in parallel with the ideal voltage source,  $v_{\tau}$ ,

Fig. 4. Schematic and small-signal model of an SGTxFB amplifier.

is ignored. The transformer model of [12] is adopted and the body effect is neglected. Initially, to simplify the mathematical analysis, inductors  $L_p$  and  $L_s$  are assumed to be ideal. However, after deriving the model, a technique to include inductor non-idealities will also be described. Applying Kirchoff's current law (KCL) to the circuit in Fig. 4 yields

$$v_{\tau} = i_p s L_p - i_s s M \tag{6a}$$

$$v_x = -i_p s M + i_s s L_s \tag{6b}$$

$$i_{\tau} = i_p + (v_{\tau} - v_x)sC_X \tag{6c}$$

$$i_s = (v_\tau - v_x)(g_m + sC_X).$$

(6d)

Solving (6a)–(6d), the input admittance  $Y_{\tau} = i_{\tau}/v_{\tau}$  can be shown to be given by (6e) as follows:

$$Y_{\tau}(s) = \frac{1}{sL_{p}(1-k^{2})} + sC_{X} - \left\{ \frac{nk}{sL_{p}(1-k^{2})} - sC_{X} \right\}$$

$$\times \frac{\left\{ \frac{\frac{k}{n}}{sL_{s}(1-k^{2})} - (g_{m} + sC_{X}) \right\}}{\left\{ \frac{1}{sL_{s}(1-k^{2})} + (g_{m} + sC_{X}) \right\}}.$$

(6e)

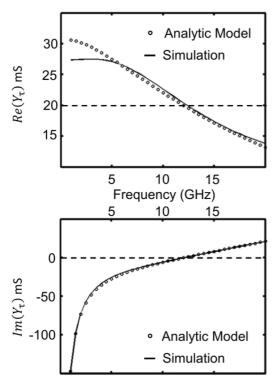

To verify (6e), a test circuit (TC1) with  $\{\omega_o, n, k, g_m, L_s\} = \{12 \text{ GHz}, 1.16, 0.5, 50 \text{ mS}, 800 \text{ pH}\}$  was designed. A comparison of  $\text{Re}(Y_\tau)$  and  $\text{Im}(Y_\tau)$  obtained from circuit simulation and from (6e) are plotted as a function of frequency in Fig. 5.

However, while (6e) is an accurate and exact solution to the KCL equations, it fails to provide insight on how to select the component values to achieve the target admittance.

To simplify (6e), the design space must be constrained as to reflect normal operating conditions. Toward this goal, a *resonance condition* is enforced: at frequency  $\omega_o$ ,  $C_X$  resonates with leakage inductance,  $L_s(1-k^2)$ . As mentioned earlier,  $C_X$  includes a shunt capacitance  $C_Z$ , which can be appropriately selected to ensure  $C_X$  satisfies the resonance condition mathematically described in (7) as follows:

$$s^{2}L_{s}(1-k^{2})C_{X} = -\omega_{o}^{2}L_{s}(1-k^{2})C_{X} = -1.$$

(7)

Fig. 5. Real and imaginary admittance: model versus circuit simulations.

Using (7), the simplifications given in (8a)–(8c) can be made

$$\left\{ \frac{nk}{sL_{p}(1-k^{2})} - sC_{X} \right\}

= \frac{n(n+k)}{j\omega_{o}L_{p}(1-k^{2})}$$

(8a)

$$\left\{ \frac{\frac{k}{n}}{sL_{s}(1-k^{2})} - (g_{m} + sC_{X}) \right\}

= \frac{(1+\frac{k}{n})}{j\omega_{o}L_{s}(1-k^{2})} - g_{m}$$

(8b)

$$\left\{ \frac{1}{sL_{s}(1-k^{2})} + (g_{m} + sC_{X}) \right\}

= g_{m}.$$

(8c)

Finally, using (8a)–(8c), a simpler expression for  $Y_{\tau}$ , (9a) and (9b),

$$Y_{\tau}(s=j\omega_{0}) = \frac{1+n(n+k)}{j\omega_{o}L_{p}(1-k^{2})} + j\omega_{o}C_{X} + \frac{(n+k)}{\omega_{o}L_{p}(1-k^{2})} \frac{(n+k)}{\omega_{o}L_{s}(1-k^{2})} \frac{1}{g_{m}}$$

(9a)

$$= \frac{1+nk}{j\omega_{o}L_{p}(1-k^{2})} + \left(\frac{C_{X}}{q_{m}L_{s}}\right) \frac{\left(1+\frac{k}{n}\right)^{2}}{(1-k^{2})}$$

(9b)

is derived. Equation (9b) has a clear physical interpretation: the input impedance of an SGTxFB amplifier appears as a parallel R-L circuit, where R and L are functions of  $\{\omega_o, n, k, g_m, L_s\}$ .

## B. Matching Network Design

Since input impedance of the SGTxFB amplifier is a function of the transformer parameters, applying transformer feedback to match the amplifier with its preceding driver stage is possible. The driver stage could be an on-chip pre-amplifier, mixer, off-chip transmission-line (T-line) driver, or antenna. To maximize the power gain of the driver stage with an output conductance  $G_s$ , a matching network is designed to ensure  $\mathrm{Re}(Y_\tau) = G_s$ . In order to match the SGTxFB amplifier to a driver with purely real admittance, all imaginary terms in (9b) must be eliminated.

Manipulating the design variables  $L_s$  and  $C_X$  to achieve cancellation of imaginary terms is not possible due to the already established resonance condition (7). Therefore, an additional capacitance  $C_Y$  must be added in parallel to  $L_p$  to achieve  $\mathrm{Im}(Y_\tau)=0$ . From (9b), it can be shown that

$$C_Y = \frac{1 + nk}{\omega_o^2 L_p (1 - k^2)}. (10)$$

After the addition of  $C_Y$ , the input admittance of the circuit is purely real and given by

$$Re(Y_{\tau}) = \frac{(n+k)}{\omega_o L_p(1-k^2)} \frac{(n+k)}{\omega_o L_s(1-k^2)} \frac{1}{g_m}.$$

(11)

Further intuition regarding the impact of feedback for bandwidth extension can be obtained by using (7) to reformulate (11), resulting as follows in (12) (derivation in Appendix II):

$$R_{\tau}(k,n) = \frac{1}{Y_{\tau}} = \left(\frac{g_m L_s}{C_X}\right) \frac{(1-k^2)}{\left(1+\frac{k}{2}\right)^2}.$$

(12)

In (12), one should notice the expression derived is similar to the input impedance of a CSA with inductor degeneration. For the circuit in Fig. 3(a), from (1), the real component of the input impedance is given by  $(g_m L_s/C_X) = R_\tau(k=0)$ . Thus, verifying that the narrowband inductor degeneration is a special case of transformer feedback. In the SGTxFB amplifier, the magnetic coupling between the windings of the transformer reduces the shunt input impedance  $R_\tau$  and provides a wideband match.

While the aforementioned results have been derived using an ideal model inductor  $L_p$  and  $L_s$ , the results can be extended to include the effects of a finite Q factor and self-resonance frequency. The loss in  $L_p$  can be modeled by a shunt resistance  $R_{pL}=Q_p\omega L_p$ , which appears in parallel with input resistance  $R_\tau$  derived in (12). The loss in  $L_s$  can be modeled as a series resistance  $R_{sL}=\omega L_s/Q_s$ . As a first-order approximation,  $R_{sL}$  can be absorbed into the amplifier transconductance by defining an effective  $g_m{}^{'}=g_m/(1+g_mR_{sL})$ . Finally, the parasitic capacitance associated with  $L_p$  and the windings between  $L_p$  and  $L_s$  can also be absorbed in capacitances  $C_Y$  and  $C_X$ , respectively.

## C. Quality Factor

A key metric for wideband matching networks is the Q factor. For a parallel RLC circuit, the quality factor is  $(R/\omega_o L)$  or

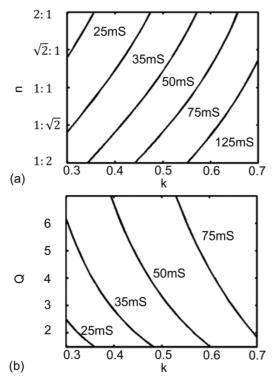

Fig. 6. Design space for matching TC1 to a 50- $\Omega$  source resistance with  $g_m=(25~{\rm mS},35~{\rm mS},50~{\rm mS},75~{\rm mS},125~{\rm mS})$  and 0.3 < k < 0.7. (a) Transformer turns-ratio. (b) Matching network Q factor.

$(\omega_o CR)$ . From the input admittance expression in (9b), the Q of the matching network can be proven to be

$$Q(s = j\omega_0) = g_m \sqrt{L_s(1 - k^2)/C_X} \frac{1 + nk}{(n + k)^2}.$$

(13)

As described earlier, the Q factor and  $\operatorname{Re}\{Y_{\tau}\}$  are functions of  $\{\omega_o, n, k, g_m, L_s\}$ . However, in order to design for  $G_s = Y_{\tau}(j\omega_o)$ , only three among  $\{n, k, g_m, L_s\}$  can be uniquely specified.  $g_m$  is primarily limited by the current budget of the target application and an upper limit on  $L_s$  is placed by the inductor's self-resonance frequency. As a result, to obtain an optimal power match, the transformer parameters  $\{n, k\}$  cannot be selected independently. Using (11) as a starting point, the following interdependence between n and k can be shown:

$$n = \frac{k}{\omega_o L_s (1 - k^2) \sqrt{\text{Re}(Y_\tau) g}_m - 1}.$$

(14)

Defining the "design space" of the circuit as all sets of  $\{n,k,g_m,L_s\}$ , which satisfy (14), the design space for the test circuit TC1, with  $L_s=800$  pH at  $\omega_o=12$  GHz, is plotted in Fig. 6. For values of  $g_m$  ranging from 25 to 125 mS, Fig. 6(a) plots n as a function of k for an SGTxFB circuit designed to match a 50- $\Omega$  driving source. Two important observations can be made from this graph. First, for a fixed turns ratio (n), an amplifier with higher current (higher  $g_m$ ) requires larger k to achieve a power match. This is important because obtaining a high k using spiral-inductor-based transformers for a non-unity turns ratio is quite challenging. Secondly, for a fixed coupling coefficient, the power match achieved by increasing values of

n is accompanied by a reduction in  $g_m$ , thereby reducing the gain of the amplifier.

Using the values of  $\{n, k\}$  obtained from (14) to solve for the Q factor of the matching network (13), a plot of the Q factor as a function of k is plotted in Fig. 6(b). As expected from the result given in (12), increasing k of the transformer, while maintaining a power match, results in a lower Q. In addition, it is interesting to note that as  $g_m$  increases, so too does the matching network Q, thereby requiring a high-k transformer for a wideband match.

#### IV. TRANSCONDUCTANCE AND NOISE

#### A. Effective Transconductance

The bandwidth extension provided by transformer feedback, described in Section III, is accompanied by a suppression of the "closed-loop" effective transconductance  $(G_m=i_d/v_\tau)$  of the SGTxFB amplifier.  $G_m$  can be derived using the small-signal model described in Fig. 4. Assuming a transistor with infinite output impedance, the short-circuit output current  $(i_d)$  of the amplifier is a product of  $g_m$  and gate-to-source voltage  $(v_\tau-v_x)$ . The relationship between the voltage at the primary  $(v_\tau)$  and secondary  $(v_x)$  of the transformer is derived in Appendix I. Using (A.3) and (7), it can be proven that  $(v_\tau-v_x)$  is inversely proportional to  $g_m$ . As a result, at  $s=j\omega_0$ ,

$$|G_m| = \frac{\left(1 + \frac{k}{n}\right)}{\omega_0 L_s (1 - k^2)}.$$

(15)

With k=0, the effective transconductance reduces to  $1/\omega_0 L_s$ . This is similar to the inductively degenerated matching network, Fig. 3(a), where

$$|G_m| = g_m Q = g_m \frac{1/\omega_0 C_X}{g_m L_S/C_X} = \frac{1}{\omega_0 L_S}.$$

(16)

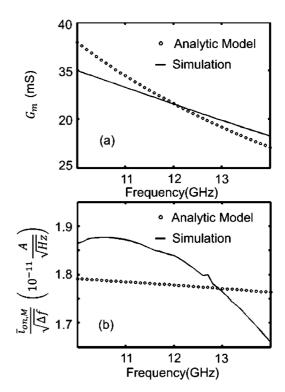

It is important to note, though  $G_m$  is not an explicit function of  $g_m$  in (15), specifying  $\{\omega_o, n, k, L_s\}$  implicitly constrains  $g_m$ . For the test circuit TC1, the  $G_m$  obtained from circuit simulation is compared with the analytic model (15) in Fig. 8(a).

Further insight regarding the relationship between  $G_m$  and  $g_m$  can be obtained by considering the expression for  $|G_m|^2$ , as given in (17). If the SGTxFB amplifier is perfectly matched to  $G_s$ , using (9a) and (17), it is straightforward to prove that  $G_m$  is the geometric mean of  $g_m$  and  $G_s$

$$|G_m|^2 = \frac{(n+k)^2}{\omega_0 L_s(1-k^2)\omega_0 L_p(1-k^2)}$$

(17)

$$|G_m| = \sqrt{g_m G_s}. (18)$$

Equation (18) offers intuition on the impact of SGTxFB loading on the gain of a two-stage amplifier. Consider a two-stage amplifier, the first being the (k-1)th stage followed by a kth stage. The input admittance of the kth stage  $(G_{s,k})$  is designed to be wideband using transformer feedback in order to provide a wideband load to the (k-1)th stage. The gain of the (k-1)th stage, {transconductance  $\cdot$  load impedance}, is inversely proportional to  $G_{s,k}$ . However, from (18),  $G_m$  or the gain of kth stage is directly proportional to  $\sqrt{G}_{s,K}$ . As a result, the cascaded gain of the kth and (k-1)th stage is only proportional to  $(1/\sqrt{G_{s,K}})$ .

Fig. 7. Small-signal model used for noise calculation.

#### B. Noise Contributions

To employ SGTxFB at the front-end of the receiver, the impact of transformer feedback on the noise performance must be considered. Two important noise contributors, thermal noise from the source resistance  $(\bar{\iota}_{\mathrm{on},Rs})$  and transistor  $M_1(\bar{\iota}_{\mathrm{on},M})$ , are considered in this section.

Assuming a driving source with an input resistance  $R_s$ , noise power  $(v_{n,Rs}^2)$ , and an SGTxFB perfectly matched to the source resistance, it is straightforward to prove that the available noise power density is  $(v_{n,Rs}^2/4)$  [13]. Using the effective transconductance defined previously, the source-induced current-noise power density  $(\bar{\tau}_{\text{on},Rs}^2)$  at the output of the SGTxFB amplifier is given by

$$\bar{t}_{\text{on},Rs}^2 = G_m^2 \frac{v_{n,Rs}^2}{4}.$$

(19)

To analyze the current noise contributed by  $M_1(\bar{\iota}_{\text{on},M})$ , consider the small-signal model in Fig. 7. The source impedance of the driver stage is modeled by the resistor  $R_s$ . Due to transformer feedback, the thermal noise in the drain current  $(i_{n,M})$  is coupled to the gate of the transistor. The resulting gate voltage noise is amplified, inverted, and fed back to the drain. The drain–current noise and the current-noise fed back via the SGTxFB are fully correlated. As a result, the inverted phase of the two noise components suppresses the output noise contribution of  $M_1$ . Applying KCL and Kirchoff's voltage law (KVL),

$$-\frac{v_{\tau}}{R} = i_p + sC_X(v_{\tau} - v_x)$$

(20a)

$$\bar{\iota}_{\text{on }M} + sC_X(v_\tau - v_x) = i_s \tag{20b}$$

$$\bar{\iota}_{\text{on},M} = g_m(v_\tau - v_x) + i_{n,M}. \tag{20c}$$

With the help of (A.1), (A.2), and (20a), it can be proven that (derived in Appendix III)

$$\bar{\iota}_{\text{on},M}^2 = \frac{i_{n,M}^2}{4 + \left(\frac{g_m}{G_m}\right)^2 \left(\frac{nk+1}{n(n+k)}\right)^2}.$$

(21)

To validate (21), the output thermal-noise power density for test circuit TC1 is calculated and compared with the noise-simulation result. The results are shown in Fig. 8(b). At 12 GHz, the output noise is modeled with an accuracy of  $\pm 5\%$  of the simulation result.

Fig. 8. (a) Effective transconductance. (b) Transistor Thermal noise contribution in TC1

C. NF

The NF of the SGTxFB amplifier is given by

$$NF = 1 + \frac{\bar{\iota}_{\text{on},M}^2}{\bar{\iota}_{\text{on},Rs}^2}.$$

(22)

Substituting, (19) and (21) in (22),

NF = 1 +

$$\left(\frac{i_{n,M}^2}{v_{n,Rs}^2}\right) \frac{1}{G_m^2 + \frac{g_m^2}{4} \left(\frac{nk+1}{n(n+k)}\right)^2}$$

. (23)

For a circuit that is perfectly matched to the source resistance  $R_s$  (conductance  $G_s$ ),  $G_m$  is governed by (18). Thus, with a source noise power,  $v_{n,Rs}^2 = 4kTR_s\Delta f$ , and drain thermal noise current,  $i_{n,M}^2 = 4kT\gamma g_m\Delta f$ ,

NF = 1 +

$$\frac{\gamma}{1 + \frac{g_m R_s}{4} \left(\frac{nk+1}{n(n+k)}\right)^2}$$

. (24)

The NF of the SGTxFB is a function of  $g_m$  and the transformer parameters (n,k). As a point of reference, consider a common-gate amplifier (CGA) and a resistor-terminated CSA with NF<sub>CGA</sub> =  $(1+\gamma)$  and NF<sub>CSA</sub> =  $(1+\gamma/g_mR_s)$ , respectively. To highlight the noise contribution of the MOSFET, a noiseless resistor termination has been assumed in the CSA.

In a CGA, the transistor  $g_m$  is uniquely specified by the admittance of the driving source, i.e.,  $g_m = 1/R_s$ . For a power-matched circuit, the minimum NF<sub>CGA</sub> is independent of  $g_m$  and only a function of  $\gamma$ . From (24), one observes that NF < NF<sub>CGA</sub> for all values of (n, k).

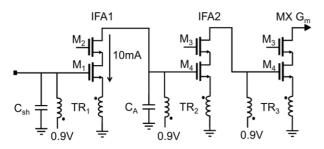

Fig. 9. Two-stage stagger-tuned IF-amplifier with SGTxFB driving the mixer transconductance (MX  $G_m$ ).

For a resistively terminated CSA, NF<sub>CSA</sub> is inversely proportional to  $g_m$ , and therefore suffers from a noise versus power tradeoff. In order to minimize the NF, the current must be maximized while maintaining power and linearity requirements. The SGTxFB relaxes this tradeoff by introducing additional design variables (n,k) via the feedback transformer. However, a qualitative comparison between the relative noise performance of the CSA and the SGTxFB amplifier is difficult because  $g_m$  is also dependent on the choice of (n,k).

In summary, analytic closed-form expressions for the input admittance, quality factor, effective transconductance, and NF have been derived in this section. As a test vehicle to validate the results, the design of a three-stage SGTxFB-based IF down-converter operating over a frequency range of 11–13 GHz is described next. The challenges involved in the design and physical implementation of a multistage SGTxFB is presented in Section V.

#### V. CIRCUIT DESIGN

#### A. IF Amplifier (IFA)

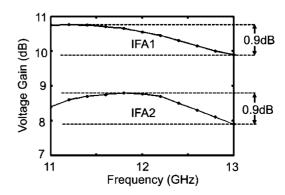

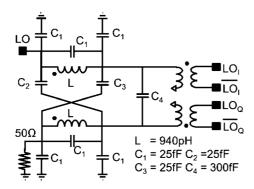

The IFA consists of two stagger-tuned SGTxFB amplifiers, IFA1 and IFA2. The circuit diagram of the IFA and mixer transconductance stage is shown in Fig. 9. In this circuit, three transformers are included for bandwidth extension. The transformer-feedback network in IFA1 is designed to match the amplifier to the 50- $\Omega$  impedance of the off-chip measurement circuitry. The overlay transformer in the input-matching network  $(TR_1)$  has a coupling coefficient of 0.7 and is formed using spiral inductors of 780 pH (Q = 14) and 2 nH (Q = 10). At the interface between IFA1 and IFA2, TR2 is designed to provide a wide-bandwidth high-gain load for IFA1. From (14), it can be observed that to increase the input impedance of IFA2, the transformer turns ratio should be increased. Thus,  $TR_2$  and  $TR_3$  are 1-to-4 transformers to maximize the gain of IFA1 and IFA2. The simulated frequency response of IFA1 and IFA2 are shown in Fig. 10. The center frequencies of IFA1 and IFA2 are tuned to 11 and 12 GHz, respectively, to reduce the in-band gain variation. Furthermore, to mitigate the impact of the cascode pole on the frequency response, transistor  $M_1$  and  $M_2$  are sized equally to allow a shared-junction layout. The gain of each stage of the amplifier varies by less than 1 dB over the 2 GHz of signal bandwidth. The two-stage IFA achieves a peak gain of 19.2 dB while consuming 20 mA of current from a 0.9-V supply.

Fig. 10. Simulated frequency response of IFA1 and IFA2.

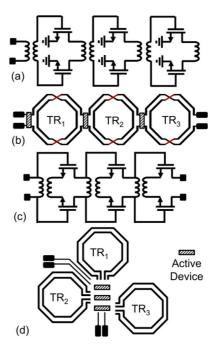

Fig. 11. Compact floor-plan for multiple transformer designs. (a) Transformer-coupled circuit. (b) Layout of multiple transformer-coupled stages. (c) Transformer-feedback circuit. (d) Layout of multiple transformer-feedback stages.

Theoretically, the gain of a generic N-stage amplifier can be increased by increasing the number of stages cascaded. However, in the case of the SGTxFB-based IFA, cascading stages becomes challenging from the perspective of unwanted parasitic elements due to the rather complicated routing between transistors and transformers from stage to stage. This problem is better illustrated by drawing a parallel between transformercoupled and transformer-feedback amplifiers. In the three-stage transformer-coupled amplifier shown in Fig. 11(a), the output of stage 1 (drain of the amplifier) and the input of stage 2 (gate of the amplifier) are completely isolated by transformer TR1. A popular technique to efficiently layout the cascaded configuration relies on using the transformer to route the output of one stage to the input of the next stage, hence the name transformer-coupled amplifiers [14], [15]; this is shown in Fig. 11(b), with the transformers between the active devices. The parasitic routing from the amplifier and transformer can be tightly controlled and minimized. Conversely, in the SGTxFB amplifier,

Fig. 12. Quadrature down-conversion IF mixer.

Fig. 11(c), both the primary and secondary of a given transformer must be routed to both the gate and source of one set of devices associated with a single stage. As a result, the standard layout from Fig. 11(b) applied to SGTxFB results in a significant amount of extra routing and a high corresponding parasitic capacitance. An alternate approach, presented in this work, minimizes the routing between the active devices and the transformers by placing the MOSFET devices of each cascaded stage in a centralized cluster, Fig. 11(d). All of the transformers are then wrapped around the clump of active devices, with the primary and secondary of each transformer oriented to facilitate transistor access. This compact layout for a cascaded SGTxFB optimizes the layout for minimal routing between stages; e.g., between IFA1, IFA2, and the mixer transconductance stage.

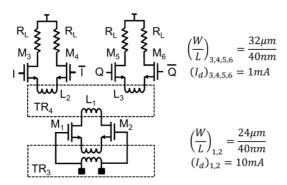

## B. IF Mixer

The output of the IFA is mixed with a 12-GHz in-phase quadrature (I/Q) local oscillator (LO) signal and down-converted to baseband. The schematic of the IF mixer is shown in Fig. 12. Two transformers, TR3 and TR4, are included within the mixer for wideband down-conversion. The SGTxFB network using transformer TR<sub>3</sub> at the interface, between the mixer transconductance-stage and IFA2, has been described earlier. The three-winding transformer (TR<sub>4</sub>) couples the output of the transconductance stage into the switching stage [16]. TR<sub>4</sub> performs two important functions. First, inductance  $L_1$  resonates with the drain-to-bulk capacitance of  $M_{1,2}$ , and  $L_2$  resonates with the device capacitance of the switching transistors  $M_{3,4,5,6}$ . Secondly, the isolation provided by TR4 prevents the flow of dc current from  $M_{1,2}$  into the switching transistors, thereby reducing the flicker-noise contribution of the switch at the baseband output. In addition, isolating the dc current from the switching stage allows for a higher load-resistance  $R_L$  and gain.

The layout of  $TR_4$  is shown in Fig. 13. An overlay transformer structure was used to increase the coupling between the inductor pairs  $L_1$ ,  $L_2$  and  $L_1$ ,  $L_3$ . Compared to the switching stage, higher current flows through the transconductance stage, thus  $L_1$  has been implemented in an UTM layer.  $L_2$  and  $L_3$  carry significantly lower switching current and have been implemented in the aluminium passivation (AP) layer.

Fig. 13. Layout of the three-winding transformer to couple the mixer transconductance and switching stages.

### C. Quadrature LO Generation

To simplify the measurement setup, quadrature LO signals for the mixer are generated on-chip using a single external 12-GHz sinusoidal signal source. Several active [17] and passive [18]–[20] techniques for generating quadrature signals have been proposed in the literature. Passive I/Q generation circuits including RC poly-phase filters and T-line-based branch line and Lange couplers are more favorable. However, both T-line and RC-based filters are associated with significant design challenges. In cases where the C values are more than an order of magnitude higher than the layout parasitics, RC poly-phase filters are suitable for I/Q generation. In contrast, T-line-based structures are better suited for frequencies above 60 GHz; frequencies at which the physical dimensions of the T-line is sufficiently small to allow implementation on-chip. At 12 GHz, the RC poly-phase implementation is highly sensitive to parasitic routing capacitances, and the T-line-based quadrature generation technique is area intensive. At the intersection of these two approaches, the lumped-element implementation of a T-line-based I/Q generator is found to be the most optimal.

Two important lumped-element coupler topologies are the branch-line and Lange coupler [20]. Branch-line couplers use only capacitive coupling, have narrower bandwidth, and require large area to ensure zero magnetic coupling between the inductors in the circuit. With the goal of optimizing area, a Lange coupler has been implemented in this design. Lange couplers use both capacitive and inductive coupling for the I/Q generation. However, to ensure the amplitude of the I and Q outputs are perfectly matched, a well-controlled magnetic coupling coefficient  $(k_m)$  is required between the inductors. Values of  $k_m$  deviating from 0.707 increase the amplitude mismatch. The schematic for the Lange coupler and balun is shown in Fig. 14. From electromagnetic (EM) simulations, LO signals have quadrature accuracy within  $\pm 0.5^{\circ}$  and an amplitude mismatch of less than 0.8 dB.

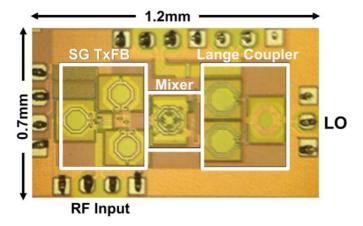

## VI. MEASUREMENT RESULTS AND COMPARISON

The chip [21] was fabricated in a six-metal-layer 40-nm CMOS process with a top level ultra-thick metal (UTM) layer. The die photograph is shown in Fig. 15 and occupies an area of 1 mm  $\times$  0.6 mm (pads included). The three transformers used for SGTxFB, the three-winding transformer in the mixer,

Fig. 14. Transformer-based lumped-element Lange coupler.

Fig. 15. Chip micrograph.

and the Lange-coupler-based quadrature generator circuit are highlighted on the chip micrograph. On-chip wafer probing was done to measure the performance. A balun probe provides a differential input signal; and a single-ended off-chip 12-GHz LO signal drives the I/Q generation circuitry.

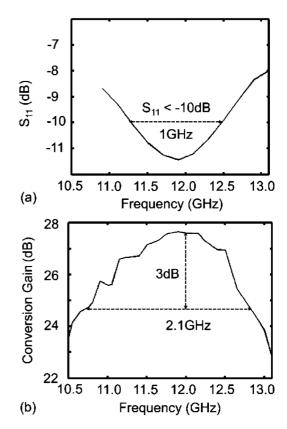

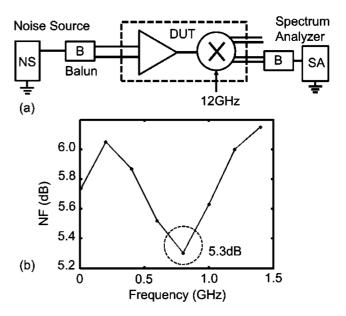

The chip consumes 30 mA of current from a 0.9-V supply. The input matching (S11) of the SGTxFB amplifier is shown in Fig. 16(a). The matching bandwidth (S11 < -10 dB) is 1 GHz. The conversion gain of the IF section is plotted as a function of frequency in Fig. 16(b). The measured peak conversion gain is 27.6 dB and the 3-dB bandwidth is 2.1 GHz. The center frequency of the IF section is at 11.6 GHz; a 400-MHz offset from the desired frequency. The NF is measured using the test setup shown in Fig. 17(a). Over the baseband signal bandwidth of 1.08 GHz, the total NF variation is less than 0.8 dB with a peak NF of 6.1 dB and a minimum of 5.3 dB. The linearity of the receiver is characterized by a two-tone test. The measured third-order intermodulation intercept point (IIP3), with two tones at 10-MHz offset from 12 GHz, is -22 dBm.

The performance of the transformer-feeedback-based wideband receiver has been compared with high fBW K-band,  $K_a$ -band and 60-GHz direct-conversion receivers in Table I. The 30% fBW UWB pulsed-radar proposed in [22] employs high-order LC bandpass filters for input and inter-stage matching. As a result, the two-stage LNA occupies an on-chip area of 0.93 mm² (estimated from a die micrograph), approximately  $8\times$  larger than the area consumed by the three transformers  $TR_1$ ,  $TR_2$ , and  $TR_3$  in Fig. 15. The two-stage

Fig. 16. (a) Input matching  $S_{11}$  (dB). (b) IF-section down-conversion gain.

Fig. 17. (a) NF measurement setup. (b) NF versus frequency.

single-ended LNA presented in [23] uses shunt peaking to achieve an fBW of 8%. In addition, the inductor-degenerated input matching-network results in narrowband input power match. References [24] and [25] propose wideband amplifiers using capactively coupled and magnetically coupled resonant tanks, respectively. While [24] achieves a gain, fBW, and NF similar to this work, [25] achieves double the fBW. However, it is important to note that [25] only includes a single-stage LNA

| Reference    | CMOS<br>Tech | V <sub>DD</sub> (V) | P <sub>DC</sub> (mW) | RF Freq<br>(GHz) | fBW<br>(%) | S <sub>11</sub> (dB) | Gain (dB)               | IIP3<br>(dBm)    | NF (dB)  |

|--------------|--------------|---------------------|----------------------|------------------|------------|----------------------|-------------------------|------------------|----------|

| [22]         | 180nm        | 1.8                 | 51ª                  | 21.3-29          | 30.6       | <-14.5               | 38.1                    | -9               | 5.5-7.4  |

| [23]         | 65nm         | N/A                 | 40.8                 | 23-25            | 8.3        | N/A                  | 31.5                    | -13              | 6.7      |

| [24]         | 65nm         | 1-1.2               | 40                   | 54-67            | 21         | <-14                 | 35.5 (high)<br>14 (low) | -39 <sup>b</sup> | 5.6-6.5  |

| [25]         | 180nm        | 1.2                 | 5.2                  | 20-30            | 40         | < -17.6              | 18.7                    | -7.6             | 7.1-14.2 |

| This<br>Work | 40nm         | 0.9                 | 28.8                 | 10.6-12.7        | 18         | < -9                 | 27.6                    | -22              | 5.3-6.2  |

TABLE I

PERFORMANCE SUMMARY AND COMPARISON WITH PRIOR ART

and has 9-dB lower gain. Cascading multiple stages to enhance the gain would result in a reduction of the bandwidth.

#### VII. CONCLUSION

Analytic expressions for the input admittance, Q factor, and NF of SGTxFB amplifiers have been derived as a function of design variables  $\{\omega_o, n, k, g_m, L_s\}$ . The impact of high and low k on the Q factor of the matching network has been described. Using transformer-feeedback-based bandwidth extension techniques, a 16% fBW IF section consisting of a two-stage stagger-tuned IF-amplifier, a transformer-coupled quadrature mixer, and a Lange coupler has been presented. The challenges associated with the layout in multistage SGTxFB are highlighted and a strategy for compact layout has been proposed.

## APPENDIX I

The primary and secondary transformer currents can be expressed as a function of  $v_{\tau}$  and  $v_{x}$  using (6a) to obtain (A.1) and (A.2),

$$i_s = \frac{\left(v_\tau \frac{k}{n} + v_x\right) s L_p}{s^2 L_p L_s (1 - k^2)} \tag{A.1}$$

$$i_p = \frac{(v_\tau + v_x nk)sL_s}{s^2 L_n L_s (1 - k^2)}.$$

(A.2)

From (A.1) and (6a), the relation between  $v_{\tau}$  and  $v_{x}$  can be expressed as

$$v_{x} = -v_{\tau} \frac{\left\{ \frac{\frac{k}{n} s L_{p}}{s^{2} L_{p} L_{s} (1 - k^{2})} - (g_{m} + s C_{X}) \right\}}{\left\{ \frac{s L_{p}}{s^{2} L_{p} L_{s} (1 - k^{2})} + (g_{m} + s C_{X}) \right\}}.$$

(A.3)

Substituting (A.2) in (6a)

$$i_{\tau} = v_{\tau} \left\{ \frac{sL_s}{s^2 L_p L_s (1 - k^2)} + sC_X \right\} + v_x \left\{ \frac{sL_s nk}{s^2 L_p L_s (1 - k^2)} - sC_X \right\}. \quad (A.4)$$

Finally, substitute (A.3) in (A.4) to obtain (6e).

#### APPENDIX II

From (9a), input admittance of the SGTxFB amplifier at the resonant frequency  $\omega_0$  is

$$Re(Y_{\tau}) = \frac{(n+k)}{\omega_o L_p(1-k^2)} \frac{(n+k)}{\omega_o L_s(1-k^2)} \frac{1}{g_m}.$$

(A.5)

Rearranging the terms in (A.5) and with  $n = \sqrt{L_p/L_s}$ ,

$$\operatorname{Re}(Y_{\tau}) = \frac{n\left(1 + \frac{k}{n}\right)}{\omega_o n^2 L_s(1 - k^2)} \frac{n\left(1 + \frac{k}{n}\right)}{\omega_o L_s(1 - k^2)} \frac{1}{g_m}.$$

(A.6)

From (A.6) and  $\{1/\omega_o^2 C_X L_p (1-k^2)\} = 1$ , it can be shown that

$$Re(Y_{\tau}(s=j\omega_0)) = \frac{\left(1 + \frac{k}{n}\right)^2}{(1 - k^2)} \frac{C_X}{L_s} \frac{1}{g_m}.$$

(A.7)

## APPENDIX III

The output noise analysis is performed using the small-signal model shown in Fig. 7. The transformer current (A.1) and (A.2) are valid even for this model. Substituting (A.1) in (20a),

$$\bar{\iota}_{\text{on},M} + sC_X(v_\tau - v_x) = \frac{\left(v_\tau \frac{k}{n} + v_x\right)}{sL_s(1 - k^2)}.$$

(A.8)

At  $s = j\omega_0$ , with the help of (7) in (A.8) can be simplified to

$$v_{\tau} = \frac{\bar{\iota}_{o,n} j \omega_0 L_s (1 - k^2)}{1 + \frac{k}{\pi}}.$$

(A.9)

Next, from (20a) and (A2),

$$-\frac{v_{\tau}}{R_s} - sC_X(v_{\tau} - v_x) = \frac{(v_{\tau} + v_x nk)}{sL_n(1 - k^2)}.$$

(A.10)

Using  $n^2=L_p/L_s$ , the terms in (A.10) can be rearranged to express  $v_x$  as a function of  $v_\tau$ . Again, using (7), it can be shown that

$$v_x = -v_\tau \frac{\left\{ (1 - n^2) + \frac{1}{R_s} j\omega_0 L_p (1 - k^2) \right\}}{(n + k)n}.$$

(A.11)

<sup>&</sup>lt;sup>a</sup> includes LNA, mixer, and VGA; <sup>b</sup> P<sub>-1</sub>dB compression point

Now, with the help of (21), (A.9), and (A.11),  $\bar{\iota}_{\text{on},M}$  is expressed as a function of  $\bar{\iota}_{n,M}$  only in (A.12c),

$$\bar{\iota}_{\text{on},M} = g_m v_\tau \left( 1 + \frac{(1 - n^2) + \frac{1}{R_s} j \omega_0 L_p (1 - k^2)}{(n + k)n} \right) + \bar{\iota}_n$$

$$(A.12a)$$

$$\bar{\iota}_{\text{on},M} = g_m \frac{\bar{\iota}_{o,n} j \omega_0 L_s (1 - k^2)}{1 + \frac{k}{n}}$$

$$\times \left( \frac{nk + 1 + \frac{1}{R_s} j \omega_0 L_p (1 - k^2)}{(n + k)n} \right) + \bar{\iota}_n$$

$$(A.12b)$$

$$\bar{\iota}_{\text{on},M} - \bar{\iota}_{\text{on},M} \left( \frac{j g_m \omega_0 L_s (1 - k^2) (nk + 1)}{(n + k)^2} \right)$$

$$- \frac{1}{R_s} \frac{g_m \omega_0 L_p (1 - k^2) \omega_0 L_s (1 - k^2)}{(n + k)^2}$$

$$= \bar{\iota}_{n,M}.$$

$$(A.12c)$$

Since the SGTxFB amplifier is perfectly matched to the source resistor  $R_s$ , using  $\text{Re}(Y_\tau)$  from (9a), it can be shown that

$$\bar{\iota}_{\text{on},M} = \frac{\bar{\iota}_{n,M}}{\left(2 - \frac{jg_m \omega_0 L_s (1 - k^2)(nk + 1)}{(n + k)^2}\right)}.$$

(A.13)

Finally, to compute the noise power,

$$\bar{\iota}_{\text{on},M}^2 = \frac{i_{n,M}^2}{4 + g_m^2 \left\{ \frac{\omega_0 L_s (1 - k^2)}{\left(1 + \frac{k}{n}\right)} \right\}^2 \left(\frac{nk+1}{n(n+k)}\right)^2}.$$

(A.14)

## ACKNOWLEDGMENT

The authors would like to thank M. Boers, P. Sen, D. J. Allstot, E. Pepine, T. Zhang, S. Dey, and A. Ravish Suvarna for many helpful discussions and comments.

#### REFERENCES

- [1] E. Laskin, M. Khanpour, S. T. Nicholson, A. Tomkins, P. Garcia, A. Cathelin, D. Belot, and S. P. Voinigescu, "Nanoscale CMOS transceiver design in the 90–170-GHz range," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 12, pp. 3477–3490, Dec. 2009.

- [2] K. Okada et al., "A 60-GHz 16QAM/8PSK/QPSK/BPSK direct-conversion transceiver for IEEE802.15.3c," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2988–3004, Dec. 2011.

- [3] A. Siligaris et al., "A 65-nm CMOS fully integrated transceiver module for 60-GHz wireless HD applications," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 3005–3017, Dec. 2011.

- [4] A. Arbabian, S. Callender, S. Kang, B. Afshar, J.-C. Chien, and A. M. Niknejad, "A 90 GHz hybrid switching pulsed-transmitter for medical imaging," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2667–2681, Dec. 2010.

- [5] J. W. May and G. M. Rebeiz, "Design and characterization of W-band SiGe RFICs for passive millimeter-wave imaging," *IEEE Trans. Mi*crow. Theory Techn., vol. 58, no. 5, pp. 1420–1430, May 2010.

- [6] A. Ismail and A. A. Abidi, "A 3–10 GHz low-noise amplifier with wideband LC-ladder matching networks," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2269–2277, Dec. 2004.

- [7] A. Bevilacqua and A. M. Niknejad, "An ultrawideband CMOS low-noise amplifier for 3.1–10.6-GHz wireless receivers," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2259–2268, Dec. 2004.

- [8] M. T. Reiha and J. R. Long, "A 1.2 V reactive-feedback 3.1–10.6 GHz low-noise amplifier in 0.13 μm CMOS," *IEEE J. Solid-State Circuits*, vol. 42, no. 5, pp. 1023–1033, May 2007.

- [9] M. Khanpour, K. W. Tang, P. Garcia, and S. P. Voinigescu, "A wide-band W-band receiver front-end in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 8, pp. 1717–1730, Aug. 2008.

- [10] A. C. Heiberg, T. W. Brown, T. S. Fiez, and K. Mayaram, "A 250 mV, 352 µW GPS receiver RF front-end in 130 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 46, no. 4, pp. 938–949, Apr. 2011.

[11] V. Bhagavatula and J. C. Rudell, "Transformer-feedback based CMOS

- [11] V. Bhagavatula and J. C. Rudell, "Transformer-feedback based CMOS amplifiers," in *IEEE Int. Circuits Syst. Symp.*, 2012, pp. 237–240.

- [12] J. R. Long, "Monolithic transformers for silicon RF IC design," *IEEE J. Solid-State Circuits*, vol. 35, no. 9, pp. 1368–1382, Sep. 2000.

- [13] J. C. Rudell, J. A. Weldon, J. J. Ou, L. Lin, and P. Gray, "An integrated GSM/DECT receiver: Design specifications," Univ. of California at Berkeley, Berkeley, CA, USA, ERL Memo UCB/ERL M97/82, 1997.

- [14] M. Boers, "A 60 GHz transformer coupled amplifier in 65 nm digital CMOS," in *IEEE RFIC Symp. Tech. Dig.*, 2010, pp. 343–346.

- [15] D. Chowdhury, P. Reynaert, and A. M. Niknejad, "Design considerations for 60 GHz transformer coupled CMOS power amplifiers," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2733–2744, Oct. 2009.

- [16] J. Paramesh, R. Bishop, K. Soumyanathan, and D. J. Allstot, "A four-antenna receiver in 90-nm CMOS for beamforming and spatial diversity," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2515–2524, Dec. 2005.

- [17] A. Rofougaran, J. Rael, M. Rofougaran, and A. Abidi, "A 900 MHz CMOS LC-oscillator with quadrature outputs," in *IEEE Int. Solid-State Circuits Tech. Dig.*, 1996, pp. 392–393.

- [18] F. Behbahani, Y. Kishigami, J. Leete, and A. A. Abidi, "CMOS mixers and polyphase filters for large image rejection," *IEEE J. Solid-State Circuits*, vol. 36, no. 6, pp. 873–887, Jun. 2001.

- [19] R. C. Frye, S. Kapur, and R. C. Melville, "A 2-GHz quadrature hybrid implemented in CMOS technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 3, pp. 550–555, Mar. 2003.

- [20] D. Ozis, J. Paramesh, and D. J. Allstot, "Integrated quadrature couplers and their applications in image-reject receivers," *IEEE J. Solid-State Circuits*, vol. 44, no. 5, pp. 1464–1476, May 2009.

- [21] V. Bhagavatula, M. Boers, and J. C. Rudell, "A transformer-feedback based wideband IF-amplifier and mixer for a heterodyne 60 GHz receiver in 40 nm CMOS," in *IEEE RFIC Symp. Tech. Dig.*, 2012, pp. 167–170.

- [22] V. Jain, S. Sundararaman, and P. Heydari, "A 22–29-GHz UWB pulseradar receiver front-end in 0.18-\(\mu\)m CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 8, pp. 1903–1914, Aug. 2009.

- [23] A. Mazzanti, M. Sosio, M. Repossi, and F. Svelto, "A 24 GHz sub-harmonic direct conversion receiver in 65 nm CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 1, pp. 88–97, Jan. 2011.

- [24] F. Vecchi *et al.*, "A wideband receiver for multi-Gbit/s communications in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 46, no. 3, pp. 551–561, Mar. 2011.

- [25] C. H. Li, C. N. Kuo, and M. C. Kuo, "A 1.2-V, 5.2-mW, 20–30 GHz wideband receiver front-end in 0.18 μm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 11, pp. 3502–3512, Nov. 2012.

Venumadhav Bhagavatula (S'10) received the B.E. degree in electronics and communication engineering from the University of Delhi, Delhi, India, in 2005, the M.Tech. degree in electronic design engineering from the Indian Institute of Science, Bangalore, India, in 2007, and is currently working toward the Ph.D. degree at the University of Washington (UW), Seattle, WA, USA.

He has held an internship with the Broadcom Corporation, Irvine, CA, USA, where he was involved with wideband millimeter-wave receivers.

Prior to joining the UW, he was an IC Designer with the Audio-Circuits Group, Cosmic Circuits Pvt. Ltd., Bangalore, India. His research interests include RF/millimeter-wave and low-power mixed-signal circuits.

Mr. Bhagavatula was the recipient of the 2007 CEDT Design Medal of the Indian Institute of Science and the 2012 Analog Devices Outstanding Student Designer Award.

**Jacques C. Rudell** (S'94–M'00–SM'09) received the B.S. degree in electrical engineering from The University of Michigan at Ann Arbor, Ann Arbor, MI, USA, and the M.S.E.E. and Ph.D. degrees from the University of California at Berkeley, Berkeley, CA, USA.

From 1989 to 1991, he was an Integrated Circuit (IC) Design Engineer with Delco Electronics (now Delphi), where his research focused mainly on bipolar analog circuits for automotive applications. From late 2000 to 2001, he was a Postdoctoral

Researcher with the University of California at Berkeley, in addition to holding consulting positions with several Silicon Valley firms. In late 2001, he joined Berkana Wireless (now Qualcomm), San Jose, CA, USA, as an Analog/RF IC Design Engineer, and later became the Design Manager of the Advanced IC Development Group. From September 2005 to December 2008, he was with the Advanced Radio Technology (ART) Group, Intel Corporation. In 2009, he joined the Faculty of Electrical Engineering as an Assistant Professor with University of Washington, Seattle, WA, USA. He is currently a member of the National Science Foundation (NSF) ERC Center for Sensorimotor Neural

Engineering (CSNE), University of Washington. His research interests are related to topics in the area of analog, RF, and mixed-signal systems. His recent areas of interest include RF and millimeter-wave circuits, in addition to interface electronic solutions toward biomedical applications.

Dr. Rudell is a member of Tau Beta Pi and Eta Kappa Nu. He was on the Technical Program Committee for the International Solid-State Circuits Conference (ISSCC) from 2003 to 2011. He is currently the 2013 general chair for the IEEE Microwave Theory and Techniques Society (IEEE MTT-S) International Microwave Symposium (IMS) and Radio Frequency Integrated Circuits (RFIC) Symposium. He is an associate editor for the IEEE JOURNAL OF SOLID-STATE CIRCUITS. He was the recipient of the 2000 Demetri Angelakos Memorial Achievement Award, a citation given to one student per year by the Electrical Engineering and Computer Science Department, University of California at Berkeley. He was the recipient of the 1998 ISSCC Jack Kilby Best Student Paper Award. He was the corecipient of the 2001 ISSCC Lewis Best Paper Award and the Best Student Paper award of the 2011 RFIC Symposium. He was also the recipient of an award presented at the 2008 ISSCC for Best Evening Session.