- MCAST reads device models written in high-level language VHDL-AMS, automatically generates simulator device codes in C, and links them directly with circuit simulator SPICE3.

- Devices read by MCAST can be transistors (such as EKV, BSIM, BSIM-SOI) or multiphysics blocks (thermal, optical, etc.).

- MCAST yields the same simulation results and comparable speed as the model code implemented manually in SPICE3-specific C code.

- MCAST also acts as a VHDL-AMS compiler and simulator, with SPICE3 acting as a simulation engine.

CAD Tools in SSRL Lab

- SILCA is targeted for fast yet accurate SPICE-level time-domain simulation of deep-submicron VLSI circuits with strong parasitic coupling effects introduced by interconnect lines, common substrate, power/ground networks, etc.

- Two novel linear-centric techniques are applied in SILCA: Semi-implicit integration predictor and iterative integration corrector are proposed for time-domain discretization.

- Nonlinear devices are represented by Piecewise Weakly NonLinear (PWNL) models. Therefore, successive variable chord method and low-rank update techniques are applied in nonlinear iteration process.

- With these techniques, SILCA reduces dramatically the number and cost of required LU factorizations. More than an order of magnitude speedup over SPICE3 has been observed for circuits with tens of thousands devices, and the efficiency increases further with the size of a circuit.

- SILCA is suitable for accurate time-domain simulation of parasitic-sensitive very large-scale integrated circuits, where the number of linear parasitic devices dominates the number of nonlinear devices. SILCA can also be used for mixed-signal circuit analysis and high fidelity coupled circuit and electromagnetic analysis.

- IPRAIL automatically retargets existing analog and RF layouts for technology migration and new specifications.

- The key contribution to the proposed approach lies in the preservation of intricacies embedded in existing layouts, which is the major concern un-addressed in. Although the layout-topologies are restricted, this method demonstrates an exiting potential in a reuse based design environment and is proved to achieve layouts comparable to manually crafted ones in quality and performance.

- For multi-GHz RF circuits, substrate-parasitics often result in significant performance degradation. Studies, supported by experiments, infer that substrate parasitics are a function of layout-patterns. Consequently, substrate models that incorporate layout effects have been developed and integrated in the IPRAIL tool-suite.

- The reuse-based layout-automation scheme presented here promises to be capable of generating layouts that are comparable in quality to manual-layouts. The technique significantly reduces design cycle time. Several layout-centric effects are modeled and incorporated into the tool-suite. High quality layouts that normally take few weeks to craft manually are generated in a few minutes. Future researches are directed towards interconnect sizing/spacing for optimization of circuit performance. This entails parasitic extraction and development of new algorithms for layout optimization with non-linear constraints.

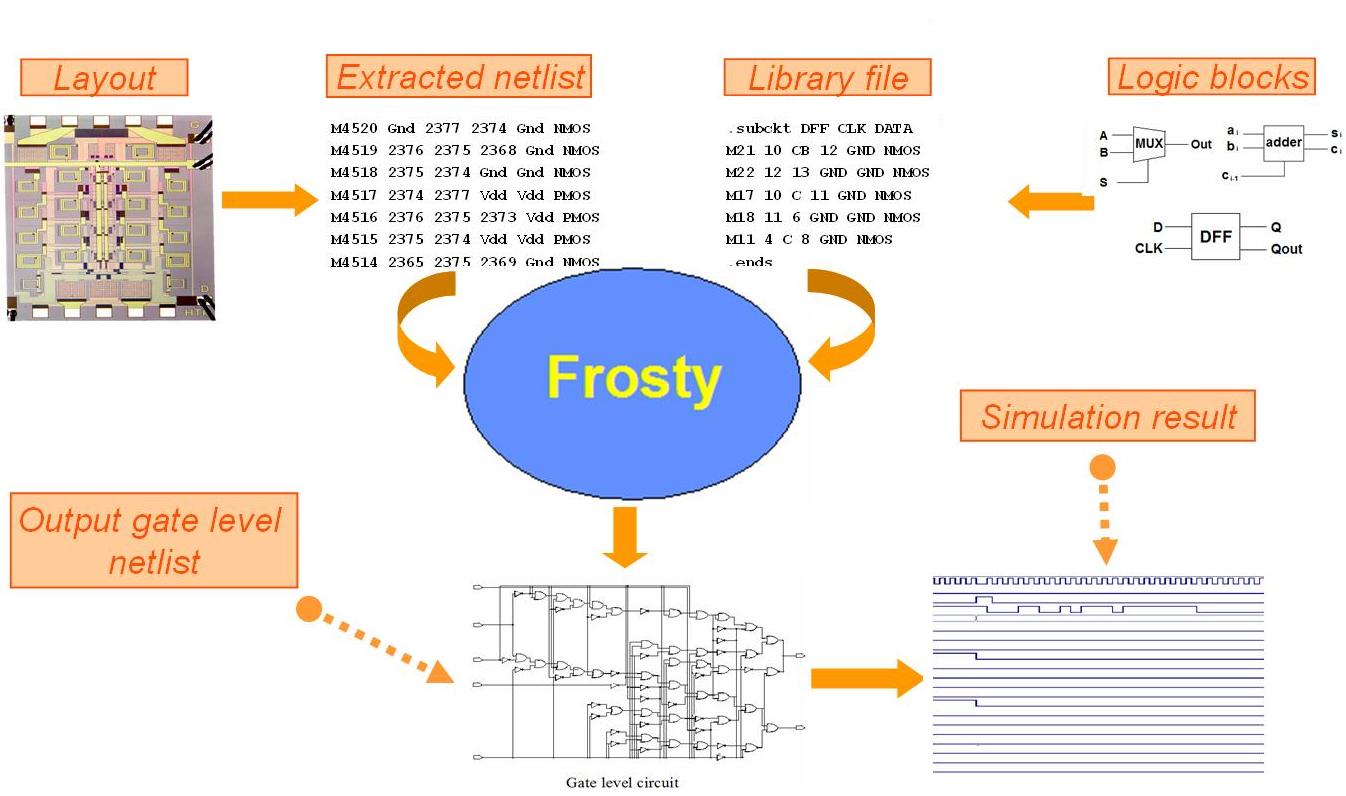

Acomputer program for automatically extracting from transistor-level netlist to a gate-level netlist.

Refer to the graph above,

- Input of FROSTY

FROSTY reads in a transistor level static CMOS netlist (object circuit), and a library file in the SPICE format. The library file contains user specified subcircuit blocks that are to be recognized from the object circuit, for example, D-flip-flop, Latch, Adder, and so on. - Two-Phase Extraction Process

FROSTY works in two phases. In Phase I, FROSTY automatically extracts all the standard CMOS gates, such as inverter, nand and nor gates. In Phase II, FROSTY extractes all the subcircuit blocks defined in the library. - Output of FROSTY

FROSTY outputs two files. One is a Verilog format gate-level netlist. Another is a header file, it contains the functional definitions of all used standard CMOS gates. Together with Verilog model descriptions of the library blocks, the extracted gate-level netlist and the header file can be simulated in any digital simulator.

Interested in Working Like Us?

Please feel free to download our working tools.

Notice: the tools are password protected. Please contact webmaster for more information.